19 data pointer control re, 20 general register (gr, e, 21 general register low by – Maxim Integrated MAXQ Family User Manual

Page 55: 22 frame pointer base regi, 19 data pointer control register (dpc, eh[4h]) -9, 20 general register (gr, eh[5h]) -9, 21 general register low byte (grl, eh[6h]) -9, 22 frame pointer base register (bp, eh[7h]) -9, Maxq family user’s guide, 19 data pointer control register (dpc, eh[4h])

4-9

MAXQ Family User’s Guide

4.19 Data Pointer Control Register (DPC, Eh[4h])

Initialization: (MAXQ10) This register is cleared to 0000h on all forms of reset.

(MAXQ20) This register is cleared to 001Ch on all forms of reset.

Access: Unrestricted direct read/write access.

4.20 General Register (GR, Eh[5h])

Initialization: This register is cleared to 0000h on all forms of reset.

Access: Unrestricted direct read/write access.

4.21 General Register Low Byte (GRL, Eh[6h])

Initialization: This register is cleared to 00h on all forms of reset.

Access: Unrestricted direct read/write access.

4.22 Frame Pointer Base Register (BP, Eh[7h])

Initialization: This register is cleared to 0000h on all forms of reset.

Access: Unrestricted direct read/write access.

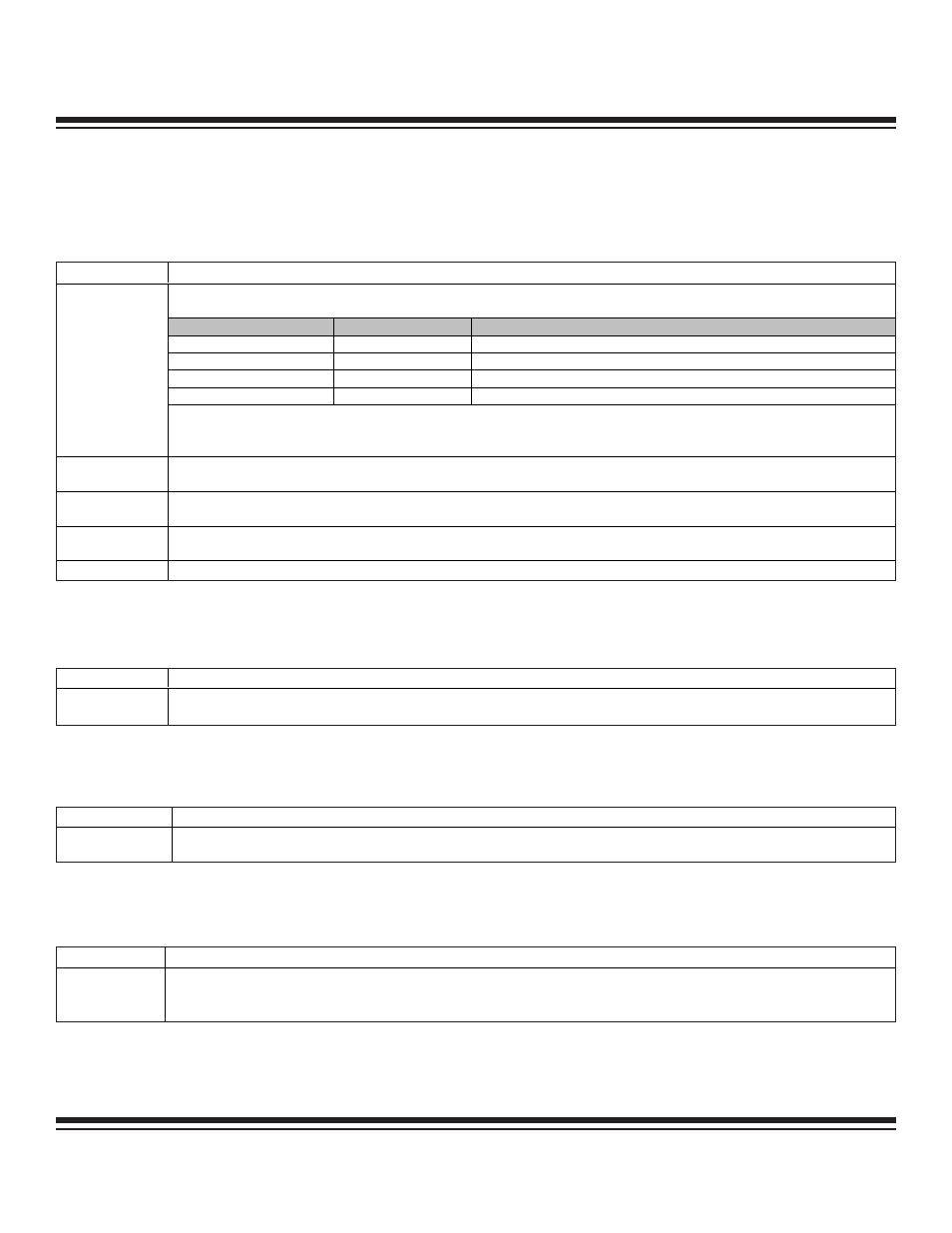

BIT

FUNCTION

Source Data Pointer Select Bits 1:0. These bits select one of the three data pointers as the active source pointer for the load

operation. A new data pointer must be selected before being used to read data memory:

SDPS1

SDPS0

SOURCE POINTER SELECTION

0

0

DP[0]

0

1

DP[1]

1

0

FP (BP[Offs])

1

1

Reserved (select FP if set)

DPC.1 to DPC.0

(SDPS1, SDPS0)

These bits default to 00b but do not activate DP[0] as an active source pointer until the SDPS bits are explicitly cleared to 00b or

the DP[0] register is written by an instruction. Also, modifying the register contents of a data/frame pointer register (DP[0], DP[1],

BP or Offs) will change the setting of the SDPS bits to reflect the active source pointer selection.

DPC.2 (WBS0)

Word/Byte Select 0. This bit selects access mode for DP[0]. When WBS0 is set to logic 1, the DP[0] is operated in word mode for

data memory access; when WBS0 is cleared to logic 0, DP[0] is operated in byte mode for data memory access.

DPC.3 (WBS1)

Word/Byte Select 1. This bit selects access mode for DP[1]. When WBS1 is set to logic 1, the DP[1] is operated in word mode for

data memory access; when WBS1 is cleared to logic 0, DP[1] is operated in byte mode for data memory access.

DPC.4 (WBS2)

Word/Byte Select 2. This bit selects access mode for BP[Offs]. When WBS2 is set to logic 1, the BP[Offs] is operated in word

mode for data memory access; when WBS2 is cleared to logic 0, BP[Offs] is operated in byte mode for data memory access.

DPC.15 to DPC.5

Reserved. Read returns 0.

BIT

FUNCTION

GR.15 to GR.0

This register is intended primarily for supporting byte operations on 16-bit data. The 16-bit register is byte-readable, byte-writeable

through the corresponding GRL and GRH 8-bit registers and byte-swappable through the GRS 16-bit register.

BIT

FUNCTION

GRL.7 to GRL.0

This register reflects the low byte of the GR register and is intended primarily for supporting byte operations on 16-bit data. Any

data written to the GRL register will also be stored in the low byte of the GR register.

BIT

FUNCTION

BP.15 to BP.0

This register serves as the base pointer for the Frame Pointer (FP). The Frame Pointer is formed by unsigned addition of Frame

Pointer Base Register (BP) and Frame Pointer Offset Register (Offs). The content of this base pointer register is not affected by

increment/decrement operations performed on the offset (OFFS) register.

Maxim Integrated