2 multiplier operand a, 2 multiplier operand a register (ma) -5, Maxq family user’s guide – Maxim Integrated MAXQ Family User Manual

Page 125: 2 multiplier operand a register (ma)

Bit 4: Square Function Enable (SQU). This bit supports the hardware square function. When this bit is set to logic 1, a square oper-

ation is initiated after an operand is written to either the MA or the MB register. Writing data to either of the operand registers writes to

both registers and triggers the specified square or square-accumulate/subtract operation. Setting this bit to 1 also overrides the OPCS

bit setting. When SQU is cleared to logic 0, the hardware square function is disabled.

0 = Square function disabled

1 = Square function enabled

Bit 3: Operand Count Select (OPCS). This bit defines how many operands must be loaded to trigger a multiply or multiply-accumu-

late/subtract operation (except when SQU = 1 since this implicitly specifies a single operand). When this bit is cleared to logic 0, both

operands (MA and MB) must be written to trigger the operation. When this bit is set to 1, the specified operation is triggered once either

operand is written.

0 = Both operands (MA and MB) must be written to trigger the multiplier operation.

1 = Loading one operand (MA or MB) triggers the multiplier operation.

Bit 2: Multiply Negate (MSUB). Configuring this bit to logic 1 enables negation of the product for signed multiply operations and sub-

traction of the product from the accumulator (MC[2:0]) when MMAC = 1. When MSUB is configured to logic 0, the product of multiply

operations will not be negated and accumulation is selected when MMAC = 1.

Bit 1: Multiply-Accumulate Enable (MMAC). This bit enables the accumulate or subtract operation (as per MSUB) for the hardware

multiplier. When this bit is cleared to logic 0, the multiplier will perform only multiply operations. When this bit is set to logic 1, the mul-

tiplier will perform a multiply-accumulate or multiply-subtract operation based upon the MSUB bit.

0 = Accumulate/subtract operation disabled

1 = Accumulate/subtract operation enabled

Bit 0: Signed-Unsigned Select (SUS). This bit determines the data type of the operands. When this bit is cleared to logic 0, the

operands are treated as two’s-complement values and the multiplier performs a signed operation. When this bit is set to logic 1, the

operands are treated as absolute magnitudes and the multiplier performs an unsigned operation.

0 = Signed operands

1 = Unsigned operands

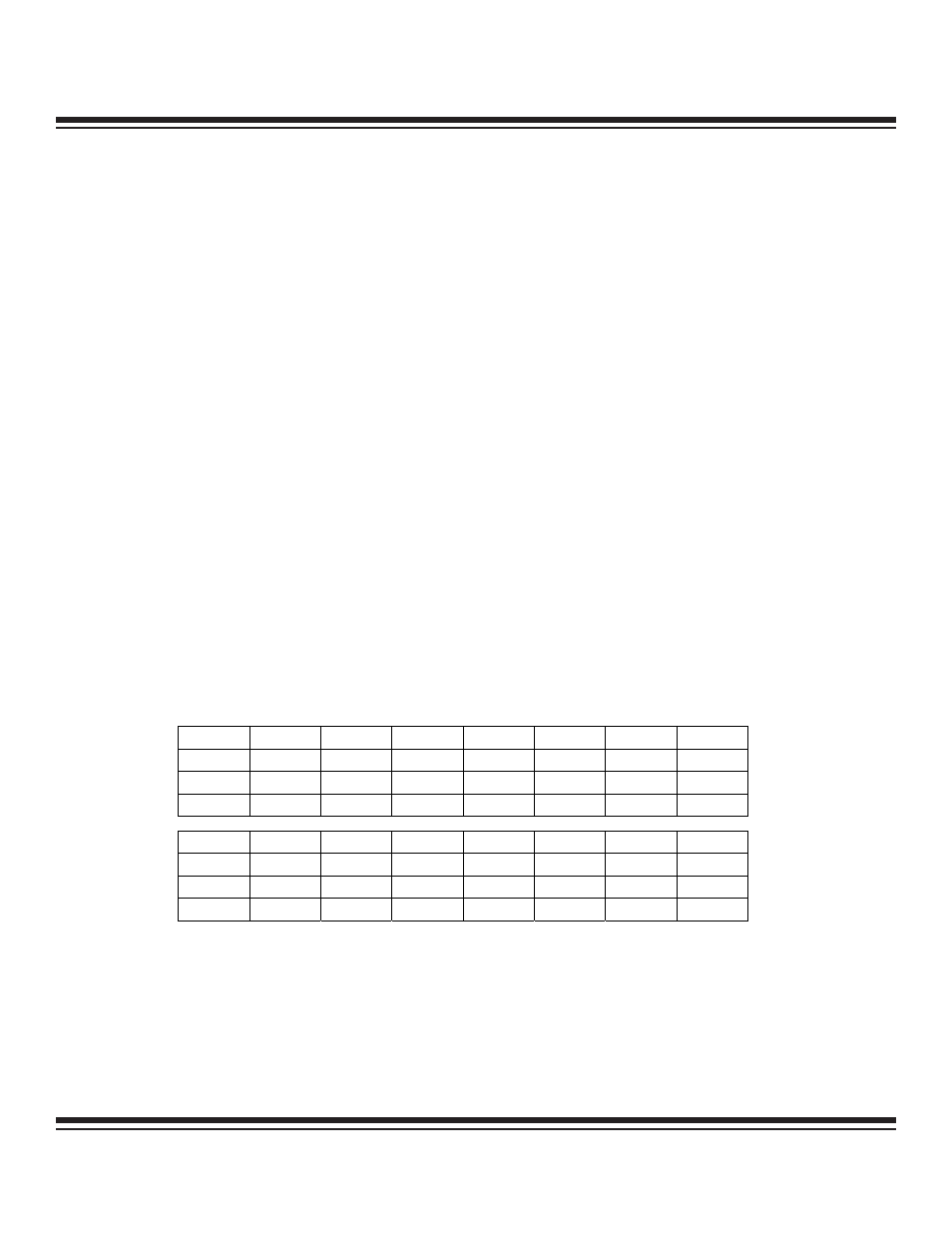

12.5.2 Multiplier Operand A Register (MA)

Bits 15 to 0: Multiplier Operand A Register (MA.[15:0]). This operand A register is used by the application code to load 16-bit val-

ues for multiplier operations.

12-5

MAXQ Family User’s Guide

Bit #

15

14

13

12

11

10

9

8

Name

MA.15

MA.14

MA.13

MA.12

MA.11

MA.10

MA.9

MA.8

Reset

0

0

0

0

0

0

0

0

Access

rw

rw

rw

rw

rw

rw

rw

rw

Bit #

7

6

5

4

3

2

1

0

Name

MA.7

MA.6

MA.5

MA.4

MA.3

MA.2

MA.1

MA.0

Reset

0

0

0

0

0

0

0

0

Access

rw

rw

rw

rw

rw

rw

rw

rw

r = read, w = write

Maxim Integrated