3 1-wire bus master control, 1 1-wire control regist, 3 1-wire bus master control -5 – Maxim Integrated MAXQ Family User Manual

Page 134: 1 1-wire control register (owa = 101b) -5, Maxq family user’s guide

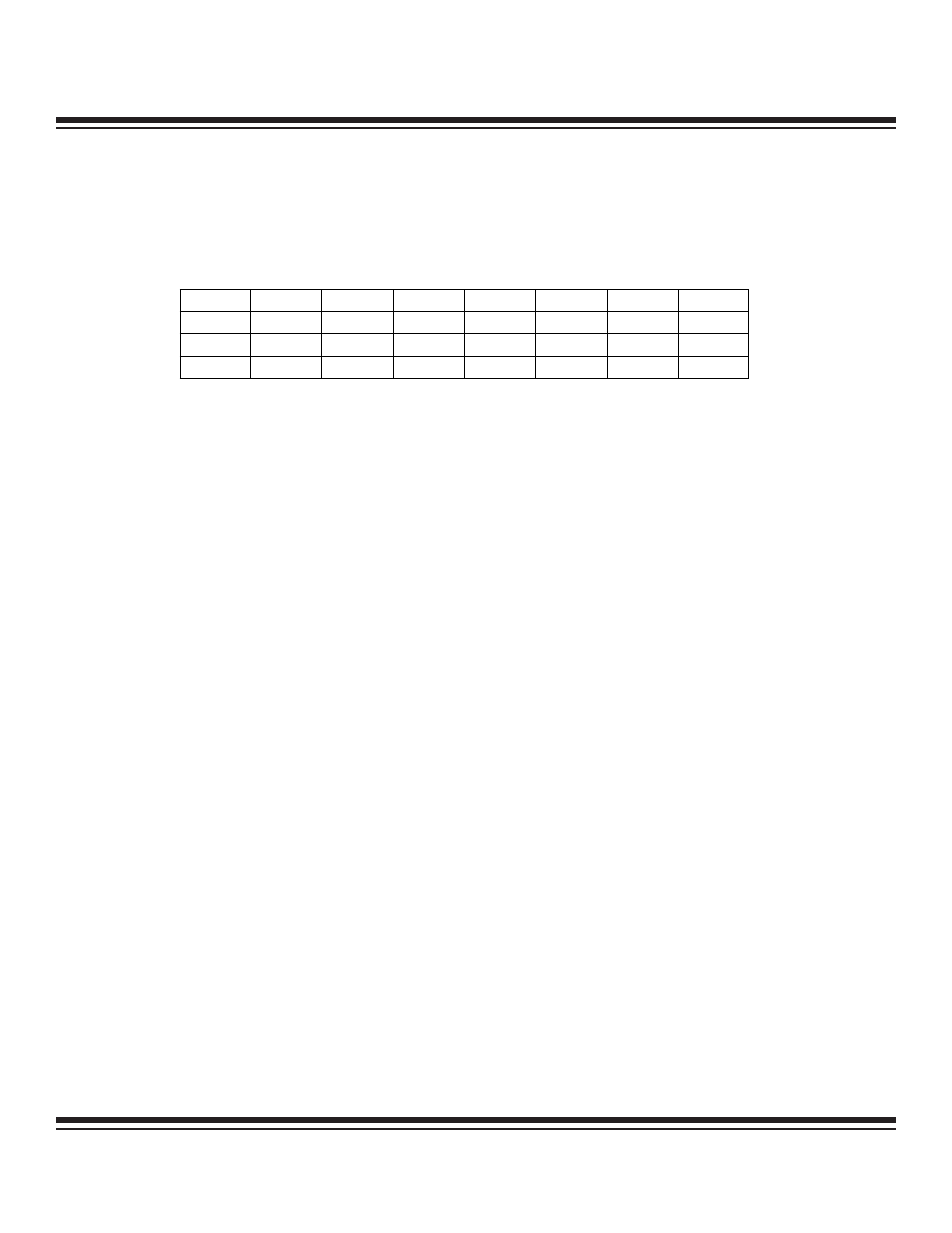

13.3 1-Wire Bus Master Control

The 1-Wire Bus Master can perform certain special functions to support OW line operation. These special functions can be set up through

the Control register that is documented below. The Control Register defaults to 00h on a reset, which disables all special functions.

13.3.1 1-Wire Control Register (OWA = 101b)

Bit 7: Enable 1-Wire Master Interrupts (EOWMI). Setting this bit to logic 1 enables the 1-Wire interrupt request to the CPU if any of

the interrupt flags in the Interrupt Flag register is set and its corresponding enable bit in the Interrupt Enable register is also set.

Clearing this bit to logic 0 disables 1-Wire interrupt request to the CPU.

Bits 6, 4, and 3: Reserved

Bit 5: Bit-Banging Mode Enable (BIT_CTL). Setting this bit to logic 1 places the master into bit-banging mode of operation, where

only the least significant bit of the transmit/receive register would be sent/received before enabling the interrupt that signals the end of

the transmission. Clearing this bit to logic 0 leaves the master operating in full byte boundaries. The Search ROM Accelerator Mode

(SRA = 1) overrides the bit-banging mode.

Bit 2: Enable Force OW (EN_FOW). To enable the force OW line command, the EN_FOW bit must be set to logic 1. Clearing this bit

to logic 0 disables the force OW line command in the command register.

Bit 1: Presence Pulse Masking (PPM). This bit is used to enable presence pulse masking function. Setting this bit to logic 1 causes

the master to initiate the beginning of a presence pulse during a 1-Wire reset. This enables the master to prevent the larger amount of

ringing caused by the slave devices when initiating a low on the OW line. If the PPM bit is set, the PDR result bit in the Interrupt Flag

Register is always set, which shows that a slave device was on the line even if there were none. Clearing this bit to logic 0 disables the

presence pulse-masking function.

Bit 0: Long Line Mode (LLM). This bit is used to enable the long line mode timing. Setting this bit to logic 1 effectively moves the write

one release and the data sample timing during standard mode communication out to 8µs and 22µs, respectively. The recovery time

will also be extended to 14ms. This provides a less strict environment for long line transmissions. Clearing this bit to logic 0 leaves the

write one release, data sampling, and recovery time during standard mode communication at 5ms, 15ms, and 10ms, respectively.

13-5

MAXQ Family User’s Guide

Bit #

7

6

5

4

3

2

1

0

Name

EOWMI

—

BIT_CTL

—

—

EN_FOW

PPM

LLM

Reset

0

0

0

0

0

0

0

0

Access

rw

r

rw

r

r

rw

rw

rw

r = read, w = write

Maxim Integrated