1 jtag bootloader operation, Maxq family user’s guide – Maxim Integrated MAXQ Family User Manual

Page 176

17-2

MAXQ Family User’s Guide

SECTION 17: IN-SYSTEM PROGRAMMING (JTAG)

Internal nonvolatile memory of MAXQ microcontrollers can be initialized via Bootstrap Loader mode. To enable the Bootstrap loader

and establish a desired communication channel, the System Programming instruction (100b) must be loaded into the TAP instruction

register using the IR-Scan sequence. Once the instruction is latched in the instruction parallel buffer (IR2:0) and is recognized by the

TAP controller in the Update-IR state, a 3-bit data shift register is activated as the communication channel for DR-Scan sequences. The

TAP retains the System Programming instruction until a new instruction is shifted in or the TAP controller returns to the Test-Logic-Reset

state. This 3-bit shift register formed between the TDI and TDO pins is directly interfaced to the 3-bit Serial Programming Buffer (SPB).

The System Programming Buffer (SPB) contains three bits with the following functions:

• SPB.0: System Programming Enable (SPE). Setting this bit to logic 1 denotes that system programming is desired upon exit-

ing reset. When it is cleared to logic 0, no system programming is needed. The logic state of SPE is examined by the reset

vector in the Utility ROM to determine the program flow after a reset. When SPE = 1, the Bootstrap Loader selected by the

PSS1:0 bits are activated to perform a Bootstrap Loader function. When SPE = 0, the Utility ROM transfers execution control

to the normal user program.

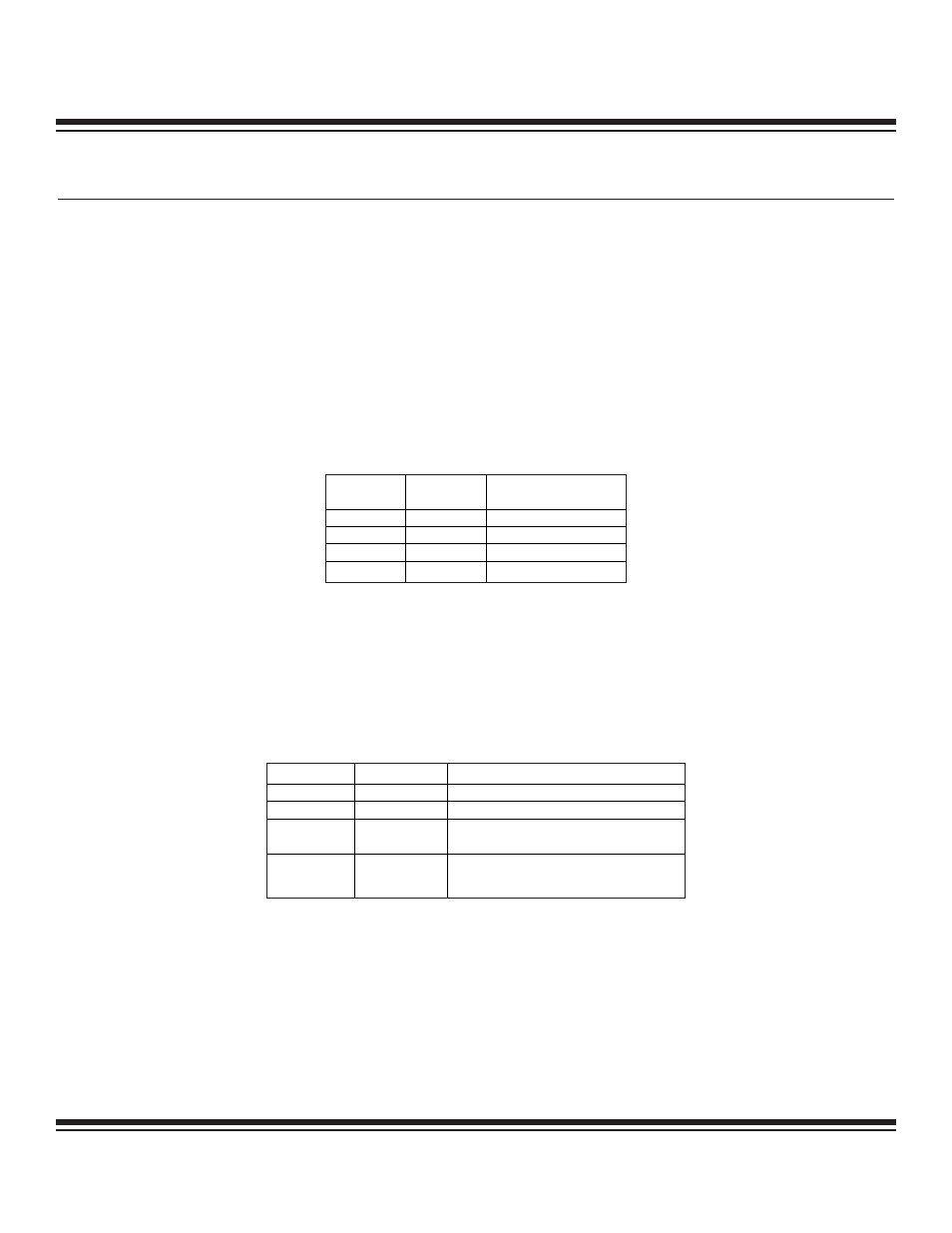

• SPB.2:1: Programming Source Select (PSS1:PSS0). These bits allow the host to select programming interface sources. The

PSS bits have no functions when the SPE bit is cleared.

The DR-Scan sequence is used to configure the SPB bits. The data content of the SPB register is reflected in the ICDF register and

allows read/write access by the CPU. These bits are cleared by power-on reset or Test-Logic-Reset of the TAP controller.

17.1 JTAG Bootloader Operation

Devices that support a JTAG bootloader have the benefit of using the same status bit handshaking hardware as is used for in-circuit

debugging. When the SPE bit of the System Programming Buffer (SPB) is set to 1 and JTAG is selected as the programming source

(PSS1:0 = 00b), the background and active debug mode state machines are disabled. Once the host loads the Debug instruction into

the TAP instruction register (IR2:0), the 10-bit shift register interface to ICDB and the status bits becomes available for host-to-ROM

bootloader communication. The status bits should be interpreted as follows for JTAG bootloader operation:

When the using the JTAG bootloader option (SPE = 1, PSS1:0 = 00b), the sole purpose of the debug hardware is to simultaneously

transfer the data byte shifted in from the host into the ICDB register and transfer the contents of an internal holding register (loaded by

ROM code writes of ICDB) into the shift register for output to the host. This transfer takes place on the falling edge of TCK at the Update-

DR state. The debug hardware additionally clears the TXC bit at this point in the state diagram. The ROM loader code controls the sta-

tus bit output to the host by asserting TXC = 1 when it has valid data to be shifted out. The ROM code may flexibly implement what-

ever communication protocol and command set it wishes within the data byte portion of the shifted 10-bit word.

PSS1

PSS0

PROGRAMMING

SOURCE

0

0

JTAG

0

1

UART

1

0

SPI

1

1

Reserved

BITS 1:0

STATUS

CONDITION

00

Reserved

Invalid condition.

01

Reserved

Invalid condition

10

Loader-Busy

ROM Loader is busy executing code

or processing the current command.

11

Loader-Valid

ROM Loader is supplying valid output

data to the host in current shift operation.

Maxim Integrated