7 1-wire bus master inter, 1 1-wire interrupt flag, 7 1-wire bus master interrupts -10 – Maxim Integrated MAXQ Family User Manual

Page 139: 1 1-wire interrupt flag register (owa = 010b) -10, Maxq family user’s guide, 7 1-wire bus master interrupts

13.7 1-Wire Bus Master Interrupts

The 1-Wire Bus Master can be configured to generate an interrupt request to the CPU on the occurrence of a number of 1-Wire relat-

ed events or conditions. These include the following: Presence Detect, Transmit Buffer Empty, Transmit Shift Register Empty, Receive

Buffer Full, Receive Shift Register Full, 1-Wire Short, and 1-Wire Low. Each of these potential 1-Wire interrupt sources has a corre-

sponding enable bit and flag bit. Each flag bit in the Interrupt Flag register (A2:A0 = 010b) is set, independent of the interrupt enable

bit, when the associated event or condition occurs. For the interrupt flag to generate an interrupt request to the CPU, the individual

enable bit for the source along with the 1-Wire Bus Master interrupt enable bit (EOWMI; Control Register bit 7) must be set to a logic

1 as well as having interrupts enabled modularly and globally. To clear the 1-Wire Bus Master Interrupt, a read of the Interrupt Flag

Register must always be performed by software. The Interrupt Enable and Interrupt Flag registers are documented below.

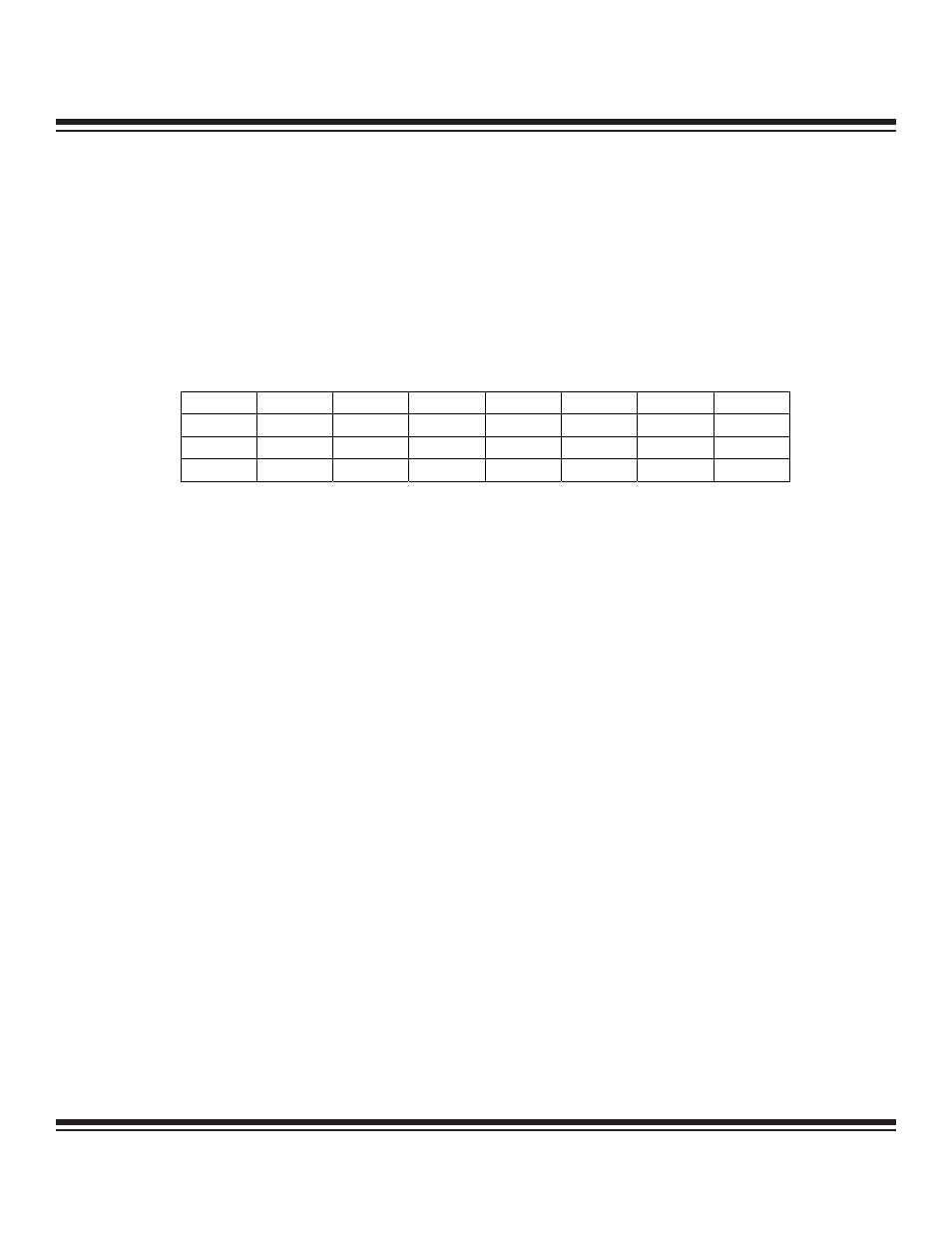

13.7.1 1-Wire Interrupt Flag Register (OWA = 010b)

Bit 7: 1-Wire Low Interrupt (OW_LOW). This flag is set to 1 when the OW line is low while the master is in idle, signaling that a slave

device has issued a presence pulse on the OW line. When this bit is 0, it shows that the OW line is high while the master is in idle. A

read to the Interrupt Flag register clears this bit if OW is no longer a low while the master is idle.

Bit 6: 1-Wire Short Interrupt (OW_SHORT). This flag is set to 1 when the OW line was low before the master was able to send out

the beginning of a reset or a time slot. When this flag is 0, it indicates that the OW line was high prior to all resets and time slots. A read

to the Interrupt Flag register clears this bit.

Bit 5: Receive Shift Register Full (RSRF). This flag is set to 1 when there is a byte of data waiting in the Receive Shift register. When

this bit is 0, it indicates that the Receive Shift register either empty or currently receiving data. This bit is cleared by the hardware when

data in the Receive Shift register is transferred to the Receive Buffer. A read to the Interrupt Flag register has no effect on this bit.

Bit 4: Receive Buffer Full (RBF). This flag is set to 1 when there is a byte of data waiting to be read in the Receive Buffer. When this

bit is 0, it indicates that the Receive Buffer has no new data to be read. This bit is cleared when the byte is read from the Receive Buffer.

A read to the Interrupt Flag register has no effect on this bit. However, following a read of the Interrupt Flag register while Enable

Receive Buffer Full Interrupt (ERBF) is set to 1, if the ERBF is not cleared and the value is not read from the Receive Buffer, the inter-

rupt will fire again.

Bit 3: Transmit Shift Register Empty (TEMT). This flag is set to 1 when there is nothing in the Transmit Shift register and is ready to

receive the next byte of data to be transmitted from the Transmit Buffer.

When this bit is 0, it indicates that the Transmit Shift Register is busy sending out data. This bit is cleared when data is transferred from

the Transmit Buffer to the Transmit Shift register. A read to the Interrupt Flag Register has no effect on this bit.

Bit 2: Transmit Buffer Empty (TBE). This flag is set to 1 when there is nothing in the Transmit Buffer and is ready to receive the next

byte of data. When it is 0, it indicates that the transmit buffer is waiting for the transmit shift register to finish sending its current data

before updating it. This bit is cleared when data is written to the Transmit Buffer. A read to the Interrupt Flag register has no effect on

this bit.

Bit 1: Presence-Detect Result (PDR). When a presence-detect interrupt occurs, this bit reflects the result of the presence detect read.

The bit is 0 if a slave device was found, or 1 if no device was found. Reading the Interrupt Flag register does not affect the state of this

bit.

Bit 0: Presence Detect (PD). After a 1-Wire reset has been issued, this flag is set to 1 after the appropriate time for a presence-detect

pulse to have occurred. This flag is 0 when the master has not recently issued a presence detect. This bit is cleared when the Interrupt

Flag register is read.

13-10

MAXQ Family User’s Guide

Bit #

7

6

5

4

3

2

1

0

Name

OW_LOW

OW_SHORT

RSRF

RBF

TEMT

TBE

PDR

PD

Reset

0

0

0

0

1

1

1

0

Access

r

r

r

r

r

r

r

r

r = read, w = write

Maxim Integrated