5 rtc alarm seconds hig, 6 rtc alarm seconds low, 5 rtc alarm seconds high register (rash) -9 – Maxim Integrated MAXQ Family User Manual

Page 150: 6 rtc alarm seconds low register (rasl) -9, Maxq family user’s guide, 5 rtc alarm seconds high register (rash), 6 rtc alarm seconds low register (rasl)

14-9

MAXQ Family User’s Guide

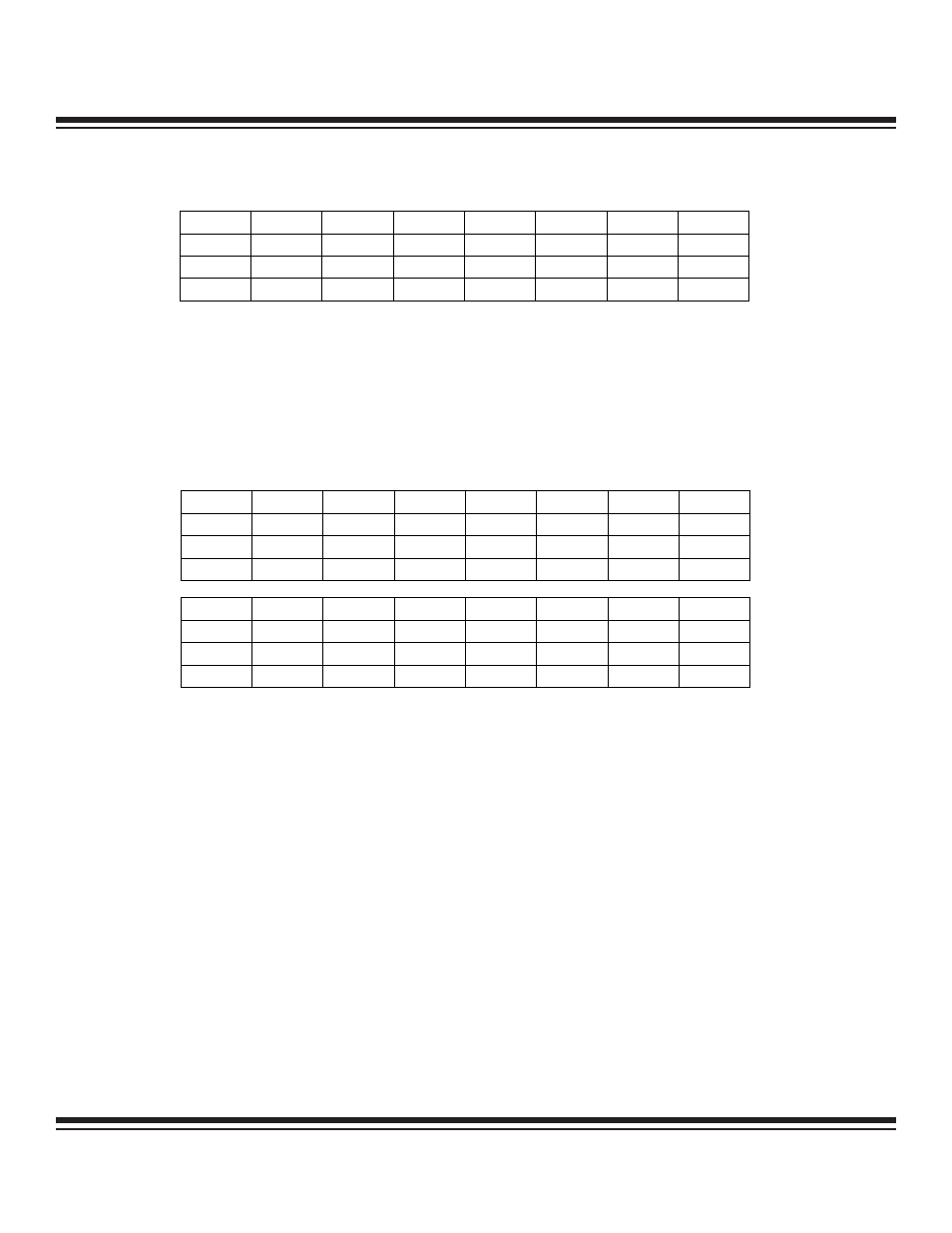

14.4.5 RTC Alarm Seconds High Register (RASH)

Bits 7 to 4: Reserved

Bits 3 to 0: RTC Alarm Seconds High (RASH.[3:0]). This register contains the most significant bits for the 20-bit time-of-day alarm.

The time-of-day alarm is formed by the RASH and the RASL registers. The 20 bits of the RASH:RASL value are compared against the

least significant 20 bits of the RTSH:RTSL seconds value for generating a time-of-day alarm. This register is write-accessible only when

ADE = 0 and BUSY = 0.

14.4.6 RTC Alarm Seconds Low Register (RASL)

Bits 15 to 0: RTC Alarm Seconds Low (RASL.[15:0]). This register contains the least significant bits for the 24-bit time-of-day alarm.

The time-of-day alarm is formed by the RASH and the RASL registers, and only the lower 20 bits are meaningful for the alarm function.

The lower 20 bits of the 24-bit RASH:RASL value are compared against the least significant 20 bits of the RTSH:RTSL seconds value

for generating a time-of-day alarm. This register is write-accessible only when ADE = 0 and BUSY = 0.

Bit #

7

6

5

4

3

2

1

0

Name

—

—

—

—

RASH.3

RASH.2

RASH.1

RASH.0

Reset

0

0

0

0

0

0

0

0

Access

r

r

r

r

rs

rs

rs

rs

r = read, s = special

Bit #

15

14

13

12

11

10

9

8

Name

RASL.15

RASL.14

RASL.13

RASL.12

RASL.11

RASL.10

RASL.9

RASL.8

Reset

0

0

0

0

0

0

0

0

Access

rs

rs

rs

rs

rs

rs

rs

rs

Bit #

7

6

5

4

3

2

1

0

Name

RASL.7

RASL.6

RASL.5

RASL.4

RASL.3

RASL.2

RASL.1

RASL.0

Reset

0

0

0

0

0

0

0

0

Access

rs

rs

rs

rs

rs

rs

rs

rs

r = read, s = special

Maxim Integrated