2 in circuit debug temp, 3 in-circuit debug cont, 2 in circuit debug temp 1 register (icdt1) -14 – Maxim Integrated MAXQ Family User Manual

Page 172: 3 in-circuit debug control register (icdc) -14, Maxq family user’s guide, 2 in-circuit debug temp 1 register (icdt1), 3 in-circuit debug control register (icdc)

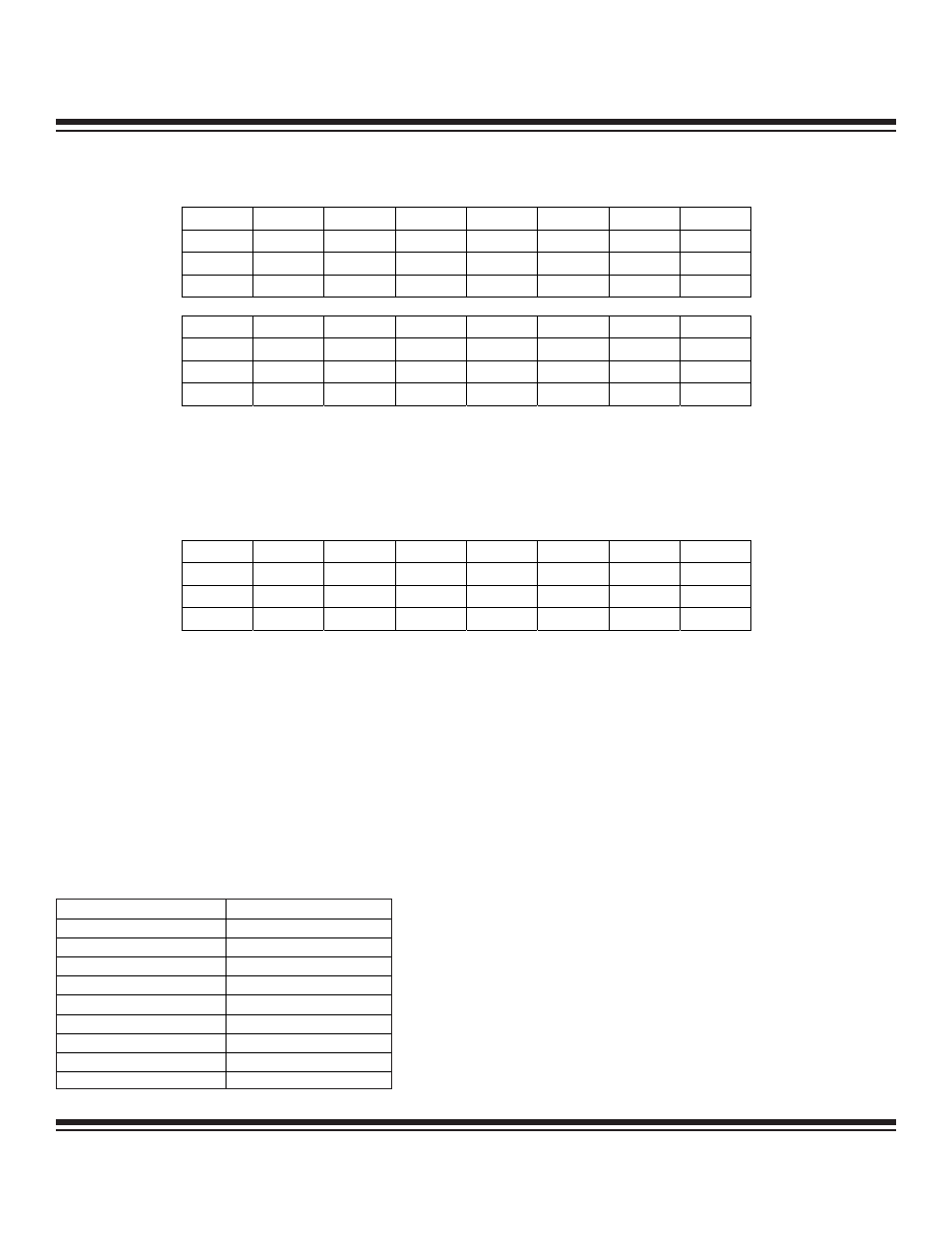

16.3.2 In-Circuit Debug Temp 1 Register (ICDT1)

Bits 15 to 0: In-Circuit Debug Temp 1 (ICDT1.[15:0]). This register is read/write accessible by the CPU only in background mode or

debug mode. This register is intended for use by the utility ROM routines as temporary storage to save registers that might otherwise

have to be placed in the stack.

16.3.3 In-Circuit Debug Control Register (ICDC)

Bit 7: Debug Mode Enable (DME). When this bit is cleared to 0, background mode commands may be executed, but breakpoints are

disabled. When this bit is set to 1, breakpoints are enabled while background mode commands still may be entered. This bit may only

be set or cleared from background debug mode. This bit has no meaning for the ROM code.

Bits 6 and 4: Reserved

Bit 5: Break-On Register Enable (REGE). The REGE bit is used to enable the break-on register function. When REGE bit is set to 1,

BP4 and BP5 are used as register breakpoints. A break occurs when the content of BP4 is matched with the destination address of

the current instruction. For BP5, a break occurs only on a selected data pattern for a selected destination register addressed by BP5.

The data pattern is determined by the contents in the ICDA and ICDD register. The REGE bit alone does not enable register break-

points, but simply changes the manner in which BP4, BP5 are used. The DME bit still must be set to a logic 1 for any breakpoint to

occur. This bit has no meaning for the ROM code.

Bits 3 to 0: Command Bits (CMD[3:0]). These bits reflect the current host command in debug mode. These bits are set by the debug

engine and allow the ROM code to determine the course of action.

16-14

MAXQ Family User’s Guide

Bit #

15

14

13

12

11

10

9

8

Name

ICDT1.15

ICDT1.14

ICDT1.13

ICDT1.12

ICDT1.11

ICDT1.10

ICDT1.9

ICDT1.8

Reset

0

0

0

0

0

0

0

0

Access

s

s

s

s

s

s

s

s

Bit #

7

6

5

4

3

2

1

0

Name

ICDT1.7

ICDT1.6

ICDT1.5

ICDT1.4

ICDT1.3

ICDT1.2

ICDT1.1

ICDT1.0

Reset

0

0

0

0

0

0

0

0

Access

s

s

s

s

s

s

s

s

s = special

Bit #

7

6

5

4

3

2

1

0

Name

DME

—

REGE

—

CMD3

CMD2

CMD1

CMD0

Reset

0

0

0

0

0

0

0

0

Access

rs

r

rs

r

rs

rs

rs

rs

r = read, s = special

CMD[3:0]

ACTION

0000

No Operation

0001

Read Register Map

0010

Read Data Memory

0011

Read Stack Memory

0100

Write Register

0101

Write Data Memory

1000

Unlock Password

1001

Read Register

Other

Reserved

Maxim Integrated