6 1-wire transmit and rec, 1 1-wire transmit/recei, 6 1-wire transmit and receive operations -9 – Maxim Integrated MAXQ Family User Manual

Page 138: 1 1-wire transmit/receive buffer (owa = 001b) -9, Maxq family user’s guide, 6 1-wire transmit and receive operations

13.6 1-Wire Transmit and Receive Operations

All data transmitted and received by the 1-Wire Bus Master passes through the transmit/receive data buffer (internal register address

A[2:0] = 001b).

The data buffer combination for the transmit interface is composed of the Transmit Buffer and Transmit Shift Register. Each of these

registers has a flag that can be used as an interrupt source. The Transmit Buffer Empty (TBE) flag is set when the Transmit Buffer is

empty and ready to accept a new byte of data from the user. As soon as the data byte is written into the Transmit Buffer, TBE is cleared.

The Transmit Shift Register Empty (TEMT) flag is set when the shift register has no data and is ready to load a new data byte from the

Transmit Buffer. When a byte of data is transferred into the Transmit Shift Register, TEMT is cleared and TBE becomes set.

To send a byte of data on the 1-Wire bus, the user writes the desired data to the Transmit Buffer. The data is moved to the Transmit

Shift Register, where it is shifted serially onto the 1-Wire bus, least significant bit first. When the Transmit Shift Register is empty, new

data will be transferred from the Transmit Buffer (if available) and the serial process repeats. Note that the 1-Wire protocol requires a

reset before any bus communication.

The data buffer combination for the receive interface is composed of the Receive Buffer and the Receive Shift Register. The receive

registers can also generate interrupts. The Receive Shift Register Full (RSRF) flag is set at the start of data being shifted into the reg-

ister, and is cleared when the Receive Shift Register is empty. The Receive Buffer Full (RBF) flag is set when data is transferred from

the Receive Shift Register into the Receive Buffer and is cleared after the CPU reads the register. If RBF is set, and another byte of

data is received in the Receive Shift Register, the Receive Shift Register will hold the new byte and wait until the user reads the Receive

Buffer, clearing the RBF flag. Thus, if both RSRF and RBF are set, no further transmissions should be made on the 1-Wire bus, or else

data may be lost, as the byte in the Receive Shift Register will be overwritten by the next received data.

To read data from a slave device, the Bus Master must first be ready to transmit data depending on commands in the Command

Register already set up by the CPU. Data is retrieved from the bus in a similar fashion to a write operation. The CPU initiates a read

operation by writing FFh data to the Transmit buffer. The data that will then be shifted into the Receive Shift Register is the wired-AND

of the Bus Master write data (FFh) and the data from the slave device. When the Receive Shift Register is full, the data is transferred

to the Receive Buffer (if RBF = 0), where the CPU can read it. Additional bytes can be read by sending FFh again. If the slave device

is not ready to respond to read request, the data received the by the Bus Master will be identical to that which was transmitted (FFh).

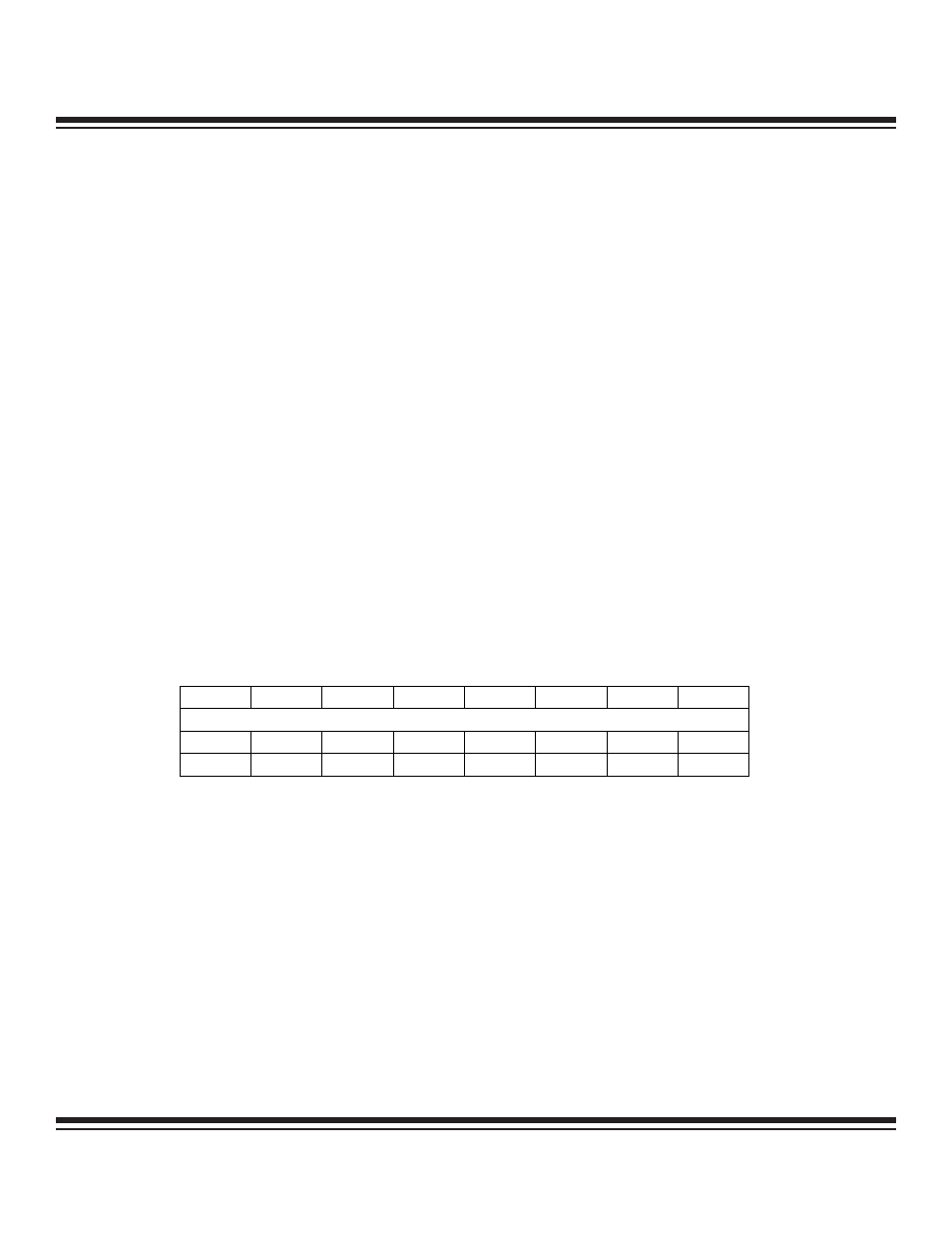

13.6.1 1-Wire Transmit/Receive Buffer (OWA = 001b)

Bits 7 to 0: 1-Wire Transmit/Receive Buffer (OWA = 001b.[7:0]). All data transmit and receive activity of the 1-Wire Bus Master pass-

es through the transmit/receive data buffer. The data buffer is double buffered with separate transmit and receive buffers. Double

buffering of the transmit buffer and receive buffer does not work when SRA (Search ROM Accelerator) mode is active. Writing to the

data buffer connects the Transmit Buffer to the data bus while reading connects the Receive Buffer to the data bus.

13-9

MAXQ Family User’s Guide

Bit #

7

6

5

4

3

2

1

0

Name

Input/Output Buffer (8 Bits)

Reset

0

0

0

0

0

0

0

0

Access

rw

rw

rw

rw

rw

rw

rw

rw

r = read, w = write

Maxim Integrated