8 system clock control reg, 8 system clock control register (ckcn, 8h[eh]) -5, Maxq family user’s guide – Maxim Integrated MAXQ Family User Manual

Page 51: 8 system clock control register (ckcn, 8h[eh])

4-5

MAXQ Family User’s Guide

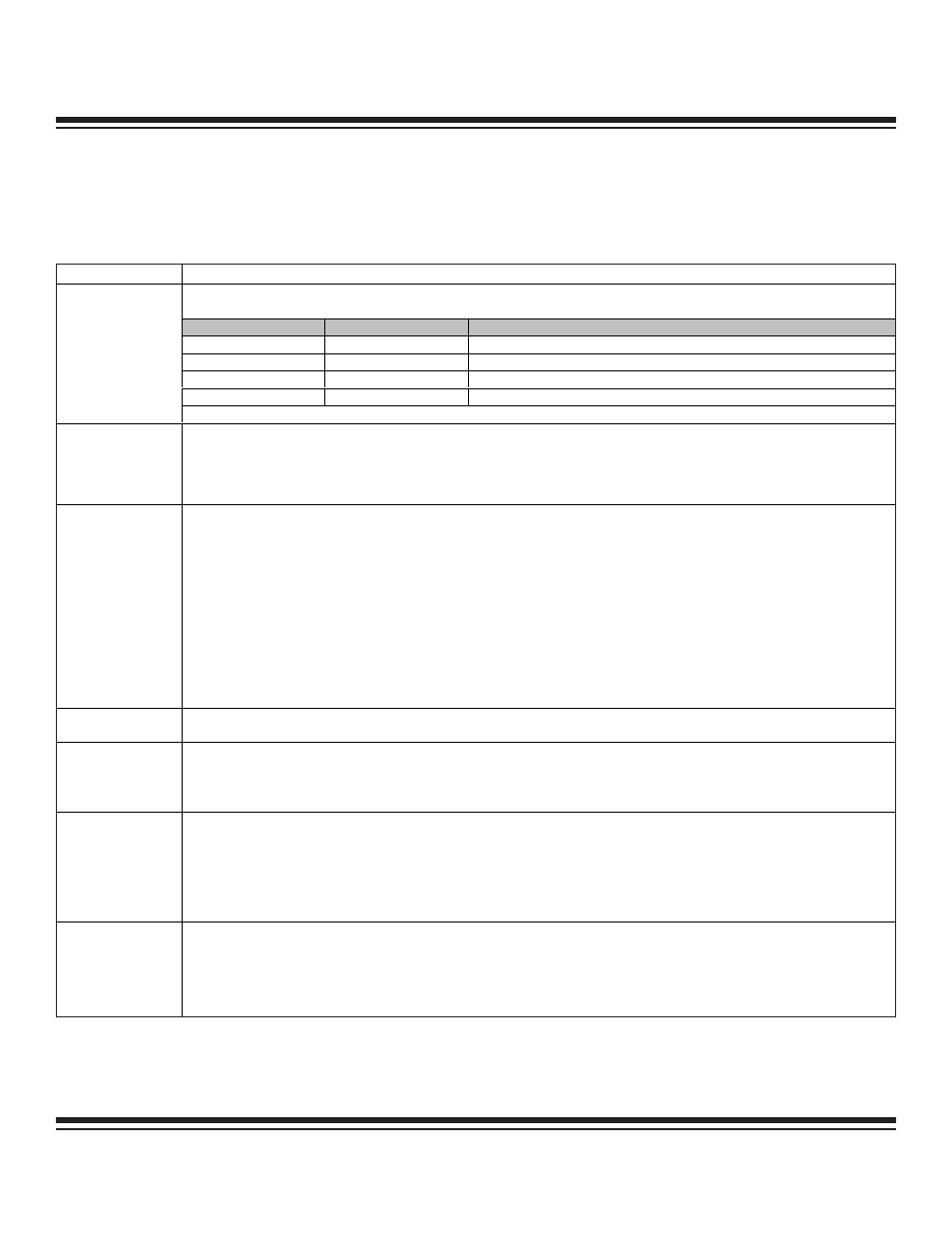

4.8 System Clock Control Register (CKCN, 8h[Eh])

Initialization: Bits 4:0 are cleared to zero on all forms of reset. See bit description for bits 7:5.

Access: Bit 5 (RGMD) is read-only. All other bits are unrestricted read/write, except for the locking mechanism on CD0 and CD1 as

described below.

BIT

FUNCTION

Clock Divide Bit 0. Clock Divide Bit 1. If the PMME bit is cleared, the CD0 and CD1 bits control the number of oscillator clocks

required to generate one system clock as follows:

CD1

CD0

OSCILLATOR CLOCK CYCLES PER SYSTEM CLOCK CYCLE

0

0

1 (default)

0

1

2

1

0

4

1

1

8

CKCN.0 (CD0);

CKCN.1 (CD1)

If the PMME bit is set to 1, the values of CD0 and CD1 may not be altered and do not affect the system clock frequency.

CKCN.2 (PMME)

Power Management Mode Enable. If the PMME bit is cleared to 0, the values of CD0 and CD1 determine the number of

oscillator clock cycles per system clock cycle. If the PMME bit is set to 1, the values of CD0 and CD1 are ignored and the

system clock operates in a fixed mode of 1 cycle per 256 oscillator cycles (divide by 256). If the PMME bit is set to 1 and

Switchback mode has been enabled (SWB = 1), when a Switchback source (such as an enabled external interrupt) becomes

active, PMME will be cleared to 0 and cannot be set to 1 unless all Switchback sources are inactive.

CKCN.3 (SWB)

Switchback Enable. If the SWB bit is cleared to 0, Switchback mode is not active. If the SWB bit is set to 1, Switchback mode is

active. Switchback mode has no effect if Power Management Mode is not active (PMME = 0). If Power Management Mode is

active and Switchback mode is enabled, the PMME bit will be cleared to 0 when any of the following conditions occur.

1) An external

interrupt condition occurs on an INTx pin and the corresponding external interrupt

is enabled.

2) An active-low transition occurs on the UART serial receive-input line (modes 1, 2, and 3) and data reception is enabled.

3) The SBUF register is written to send an outgoing byte through the UART and transmission is enabled

4) The SPIB register is written in master mode (STBY = 1) to send an outgoing character through the SPI module and

transmission is enabled.

5) The SPI module’s SSEL signal is asserted in slave mode.

6) Time-of-Day and Subsecond interval alarms from the RTC when enabled.

7) Active debug mode is entered either by break point match or issuance of the 'Debug' command from background mode.

When any of these conditions cause Switchback to clear PMME to 0, the system clock rate will then be determined by the

settings of CD0 and CD1. After PMME is cleared to 0 by Switchback, it may not be set back to 1 as long as any of the above

conditions are true.

CKCN.4 (STOP)

Stop Mode Select. Setting this bit to 1 causes the MAXQ to enter Stop Mode. This will not change the currently selected clock

divide ratio (CD0, CD1, PMME).

CKCN.5 (RGMD)

Ring Oscillator Mode. This read-only bit reflects the selection of clock source. RGMD = 1 indicates the ring oscillator is

providing the system clock. RGMD = 0 indicates that the clock source specified by the XT/RC bit is being used for system clock

generation. If the given MAXQ device does not include an internal ring oscillator from which it can run, this read-only bit will

track the value of CKCN.6.

CKCN.6 (RGSL)

Ring Oscillator Select. This bit selects the internal ring oscillator for system clock generation. When RGSL is set to 1, the internal

ring oscillator (following the PMME, CD1:0 selected divide ratio) is immediately sourced as the system clock and the internal

crystal amplifier is disabled (if allowed). When RGSL is cleared to 0, the internal ring oscillator (following the clock divide

selection) will continue to serve as the system clock until the warm-up counter associated with the XT/RC clock selection has

expired. At which point, that clock source (following the PMME, CD1:0 selected divide ratio) is sourced as the system clock.

The RGSL bit is cleared to 0 on power-on reset only and is unaffected by other resets. If the given MAXQ device does not

include an internal ring oscillator from which it can run, this bit can be used as a general-purpose read/write bit.

CKCN.7(XT/RC)

Crystal/RC Oscillator Select. This bit selects the non-ring oscillator mode that may be used for system clock generation. The XT/

RC bit can only be modified when RGSL = 1. The XT/ RC bit is set to 1 on power-on reset only and is unaffected by other resets.

XT/ RC = 0: external RC configuration

XT/ RC = 1: external crystal/clock configuration

If the given MAXQ device does not support both the crystal and RC options, this bit can be used as a general-purpose

read/write bit that is write protected when CKCN.6 is configured to 0.

Maxim Integrated