7 breakpoint 5 regist, 8 breakpoint 5 regist, 7 breakpoint 5 register (bp5) (rege = 0) -8 – Maxim Integrated MAXQ Family User Manual

Page 166: 8 breakpoint 5 register (bp5) (rege = 1) -8, Maxq family user’s guide

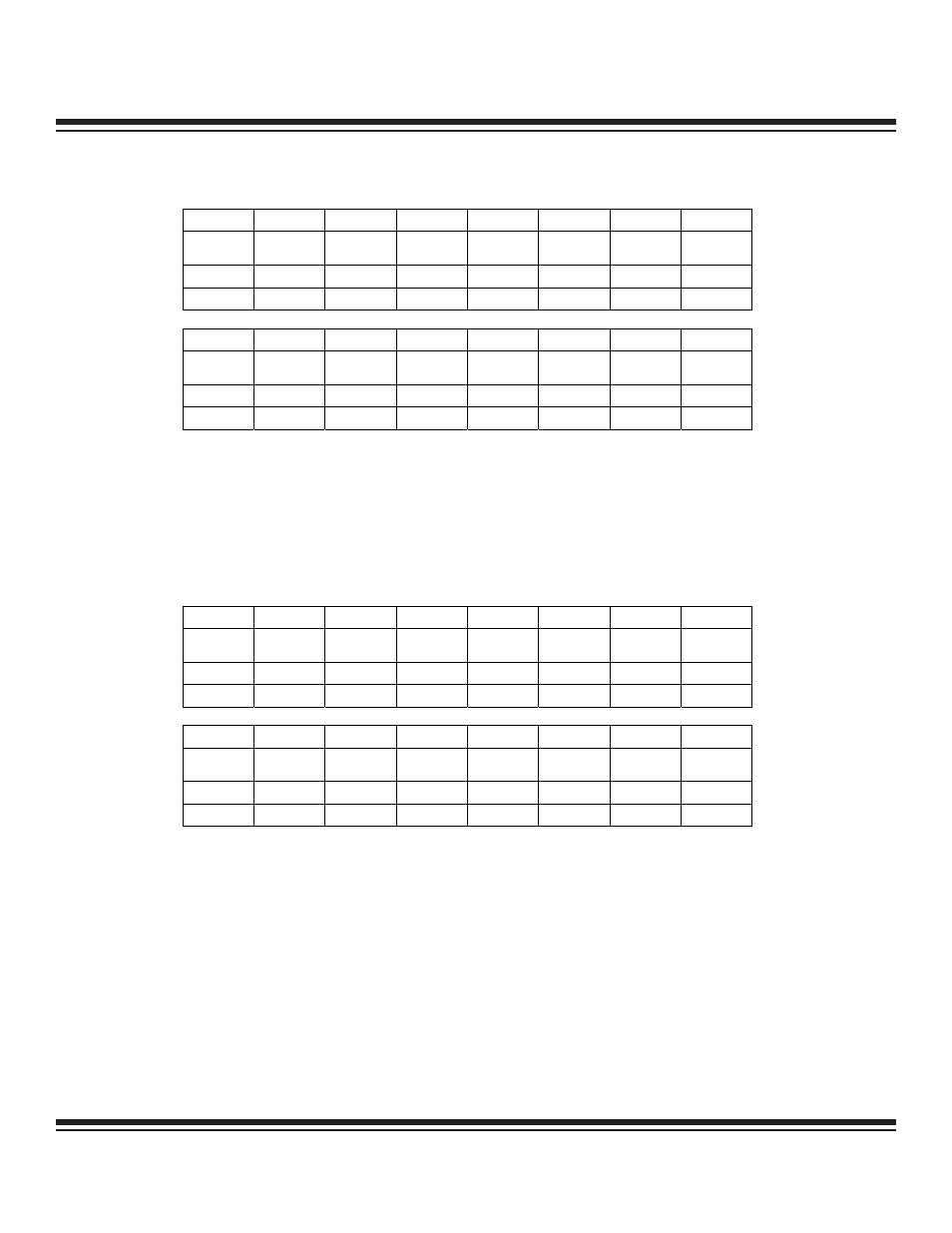

16.1.1.7 Breakpoint 5 Register (BP5) (REGE = 0)

Bits 15 to 0: Breakpoint 5 (BP5.[15:0]). This register is accessible only via background mode read/write commands.

(REGE = 0) This register serves as one of the two data memory address breakpoints. When DME is set in background mode, the debug

engine will monitor the data memory address bus activity while the CPU is executing the user program. If an address match is detect-

ed, a break occurs, allowing the debug engine to take over control of the CPU and enter debug mode.

16.1.1.8 Breakpoint 5 Register (BP5) (REGE = 1)

Bits 15 to 9: Reserved

Bits 8 to 0: Breakpoint 5 (BP5.[8:0]). This register is accessible only via background mode read/write commands.

(REGE = 1) This register serves as one of the two register breakpoints. A break occurs when two conditions are met:

Condition 1: The destination register address for the executed instruction matches with the specified module and index.

Condition 2: The bit pattern written to the destination register matches those bits specified for comparison by the ICDD data register

and ICDA mask register. Only those ICDD data bits with their corresponding ICDA mask bits will be compared. When all bits in the

ICDA register are cleared, Condition 2 becomes a don’t care.

16-8

MAXQ Family User’s Guide

Bit #

15

14

13

12

11

10

9

8

Name

(REGE = 0)

BP5.15

BP5.14

BP5.13

BP5.12

BP5.11

BP5.10

BP5.9

BP5.8

Reset

1

1

1

1

1

1

1

1

Access

s

s

s

s

s

s

s

s*

Bit #

7

6

5

4

3

2

1

0

Name

(REGE = 0)

BP5.7

BP5.6

BP5.5

BP5.4

BP5.3

BP5.2

BP5.1

BP5.0

Reset

1

1

1

1

1

1

1

1

Access

s*

s*

s*

s*

s**

s**

s**

s**

s = special, * = register index within module {0-31), ** = module specifier 3:0 {0-15}

Bit #

15

14

13

12

11

10

9

8

Name

(REGE = 1)

—

—

—

—

—

—

—

BP5.8

Reset

1

1

1

1

1

1

1

1

Access

s

s

s

s

s

s

s

s*

Bit #

7

6

5

4

3

2

1

0

Name

(REGE = 1)

BP5.7

BP5.6

BP5.5

BP5.4

BP5.3

BP5.2

BP5.1

BP5.0

Reset

1

1

1

1

1

1

1

1

Access

s*

s*

s*

s*

s**

s**

s**

s**

s = special, * = register index within module {0-31), ** = module specifier 3:0 {0-15}

Maxim Integrated