11 using the watchdog timer, 11 using the watchdog timer -17, Maxq family user’s guide – Maxim Integrated MAXQ Family User Manual

Page 42: Table 3-2. watchdog timer register control bits

3-17

The following data pointer related instructions are invalid:

move @++DP[0], @DP[0]++

move @++DP[1], @DP[1]++

move @BP[++Offs], @BP[Offs++]

move @--DP[0], @DP[0]--

move @--DP[1], @DP[1]--

move @BP[--Offs], @BP[Offs--]

move @++DP[0], @DP[0]--

move @++DP[1], @DP[1]--

move @BP[++Offs], @BP[Offs--]

move @--DP[0], @DP[0]++

move @--DP[1], @DP[1]++

move @BP[--Offs], @BP[Offs++]

move @DP[0], @DP[0]++

move @DP[1], @DP[1]++

move @BP[Offs], @BP[Offs++]

move @DP[0], @DP[0]--

move @DP[1], @DP[1]--

move @BP[Offs], @BP[Offs--]

move DP[0], @DP[0]++

move DP[0], @DP[0]--

move DP[1], @DP[1]++

move DP[1], @DP[1]--

move Offs, @BP[Offs--]

move Offs, @BP[Offs++]

3.11 Using the Watchdog Timer

The Watchdog Timer is a user-programmable clock counter that can serve as a time-base generator, an event timer, or a system super-

visor. As can be seen in the diagram below, the timer is driven by the main system clock and is supplied to a series of dividers. If the

watchdog interrupt and the watchdog reset are disabled (EWDI = 0 and EWT = 0), the watchdog timer and its input clock are disabled.

Whenever the watchdog timer is disabled, the watchdog interval timer (per WD1:0 bits) and 512 clock reset counter will be reset if either

the interrupt or reset function is enabled. When the watchdog timer is initially enabled, there will be a 1-clock to 3-clock cycle delay before

it starts. The divider output is selectable, and determines the interval between timeouts. When the timeout is reached, an interrupt flag is

set, and if enabled, an interrupt occurs. A watchdog-reset function is also provided in addition to the watchdog interrupt. The reset and

interrupt are completely discrete functions that can be acknowledged or ignored, together or separately for various applications.

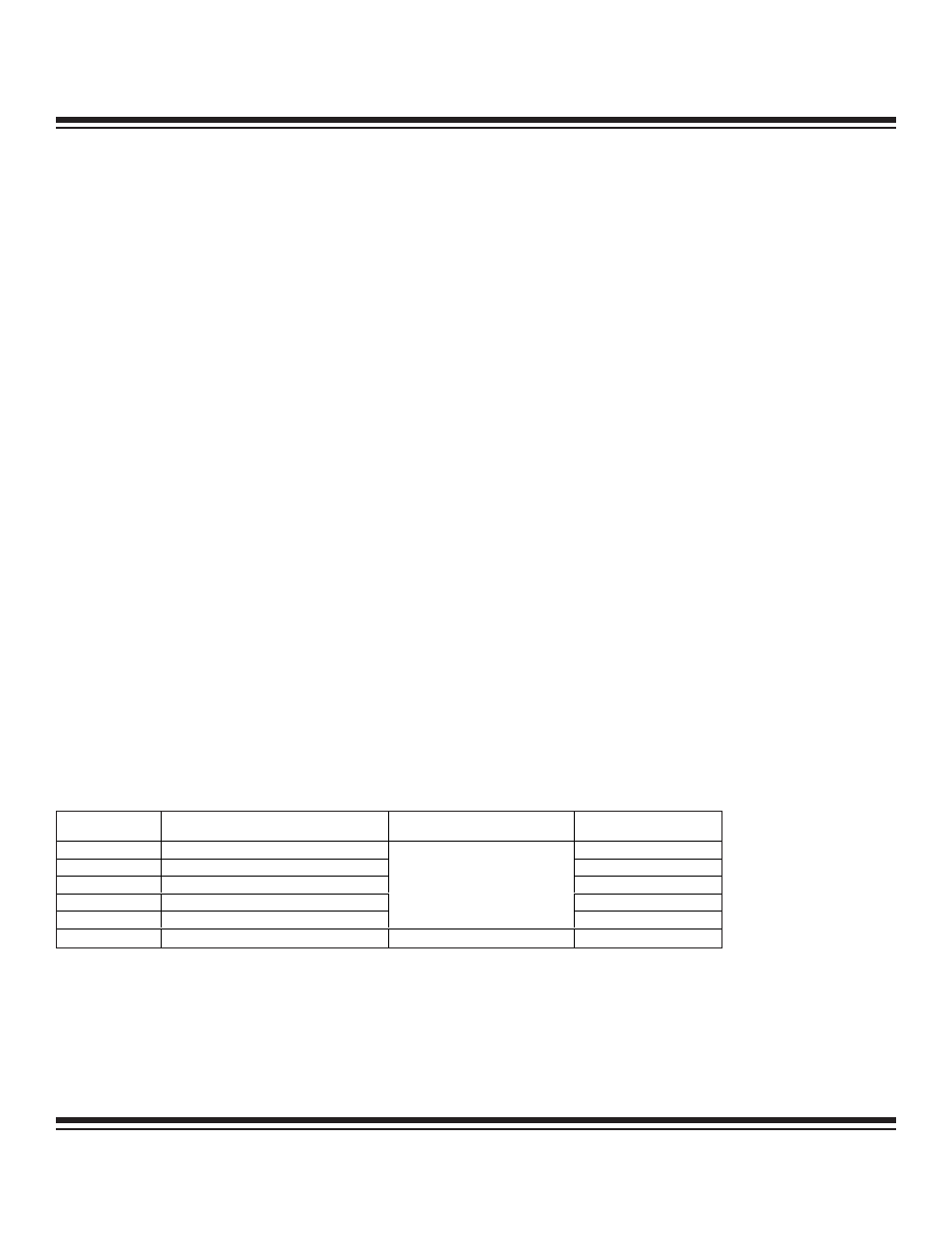

Table 3-2. Watchdog Timer Register Control Bits

The Watchdog Timer Reset function works as follows. After initializing the correct timeout interval (discussed below), software can

enable, if desired, the reset function by setting the Enable Watchdog Timer Reset (EWT = WDCN.1) bit. Setting the EWT bit will

reset/restart the Watchdog timer if the Watchdog interrupt is not already enabled. At any time prior to reaching its user selected termi-

nal value, software can set the Reset Watchdog Timer (RWT = WDCN.0) bit. If the Watchdog Timer is reset (RWT bit written to a logic

1) before the timeout period expires, the timer will start over. Hardware will automatically clear RWT after software sets it.

BIT NAME

DESCRIPTION

REGISTER LOCATION

BIT POSITION

EWDI

Enable Watchdog Timer Interrupt

WDCN.6

WD1, WD0

Watchdog Interval Control Bits

WDCN.5,4

WDIF

Watchdog Interrupt Flag

WDCN.3

WTRF

Watchdog Timer Reset Flag

WDCN.2

EWT

Enable Watchdog Timer Reset

WDCN (Fh, 8h)

WDCN.1

RWT

Reset Watchdog Timer

WDCN.0

MAXQ Family User’s Guide

Maxim Integrated