5 i/o port peripheral regi, 1 port output x register, 2 port input x register – Maxim Integrated MAXQ Family User Manual

Page 61: 3 port direction x regis, 5 i/o port peripheral registers -4, 1 port output x register (pox) -4, 2 port input x register (pix) -4, 3 port direction x register (pdx) -4, Maxq family user’s guide, 5 i/o port peripheral registers

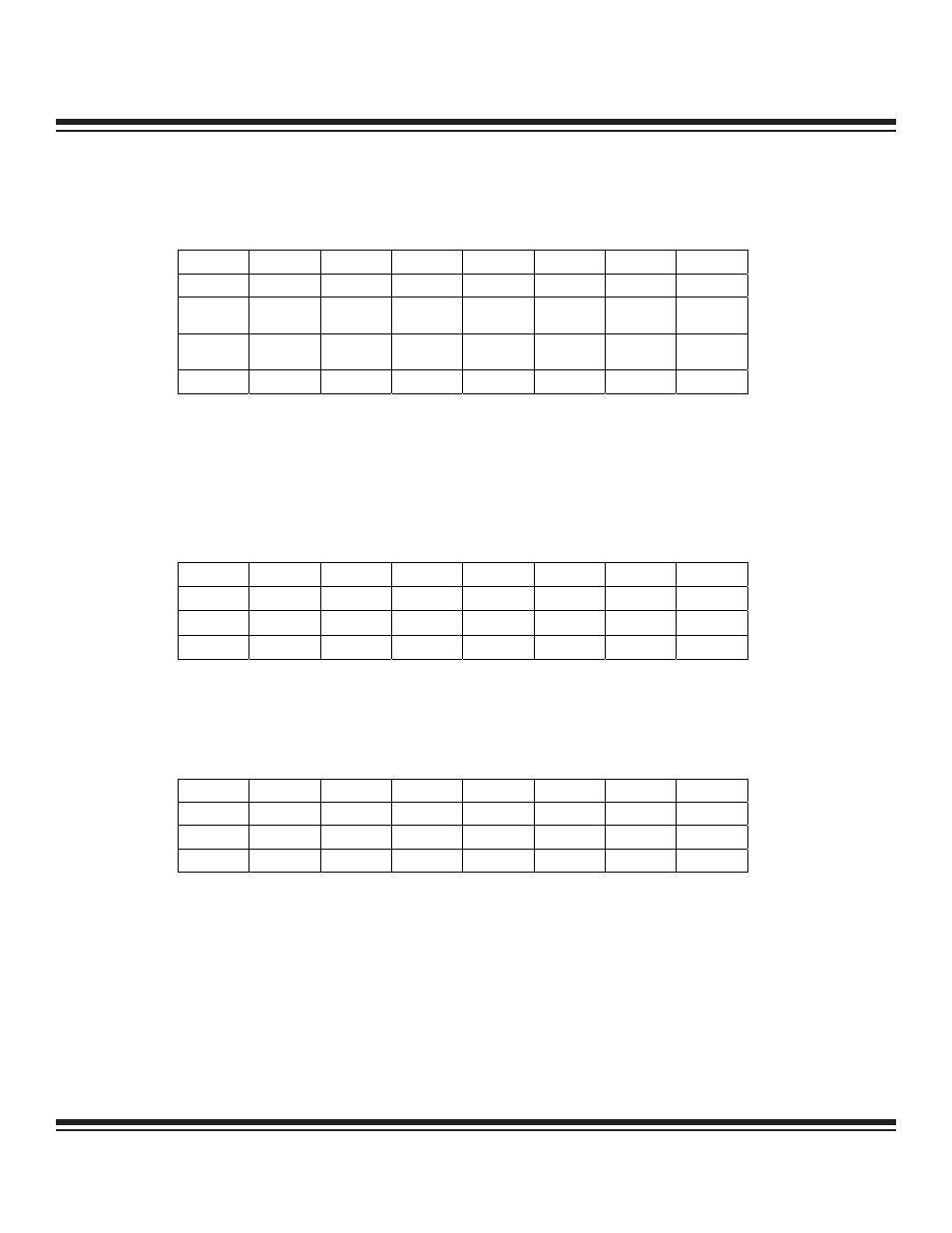

6.5 I/O Port Peripheral Registers

6.5.1 Port Output x Register (POx)

Bits 7 to 0: Port Output x (POx) (POx.[7:0]). This register stores the data that is output on any of the pins of Port x that have been defined

as output pins. Changing the data direction of any pins for this port (through register PDx) will not affect the value in this register.

If Port x is a Type C or Type D port that supports the weak pullup input mode, the POx register bits control the weak pullup enables for

any port pins that have been configured as input pins.

6.5.2 Port Input x Register (PIx)

Bits 7 to 0: Port Input x (PIx) (PIx.[7:0]). The PIx register always reflects the logical state of its pins when read.

6.5.3 Port Direction x Register (PDx)

Bits 7 to 0: Port Direction x (PDx) (PDx.[7:0]). This register is used to determine the direction of the Port x function. The port pins are

independently controlled by their direction bit. When a bit is set to 1, its corresponding pin is used as an output, causing data in the

respective POx register bit to be driven on the pin.

For Type A and Type B ports, when a bit is cleared to 0, its corresponding pin becomes a tri-stated input, allowing and external signal

to drive the pin.

For Type C and Type D ports, when a bit is cleared to 0, its corresponding pin becomes an input that can be weakly pulled up (if the

respective PO bit = 1) or can be tri-stated (if the respective PO bit = 0).

6-4

MAXQ Family User’s Guide

Bit #

7

6

5

4

3

2

1

0

Name

POx.7

POx.6

POx.5

POx.4

POx.3

POx.2

POx.1

POx.0

Reset (Type A

or Type B)

0

0

0

0

0

0

0

0

Reset (Type C

or Type D)

1

1

1

1

1

1

1

1

Access

rw

rw

rw

rw

rw

rw

rw

rw

r = read, w = write

Bit #

7

6

5

4

3

2

1

0

Name

PDx.7

PDx.6

PDx.5

PDx.4

PDx.3

PDx.2

PDx.1

PDx.0

Reset

0

0

0

0

0

0

0

0

Access

rw

rw

rw

rw

rw

rw

rw

rw

r = read, w = write

Bit #

7

6

5

4

3

2

1

0

Name

PIx.7

PIx.6

PIx.5

PIx.4

PIx.3

PIx.2

PIx.1

PIx.0

Reset

s

s

s

s

s

s

s

s

Access

r

r

r

r

r

r

r

r

r = read, s = special

Maxim Integrated