2 timer/counter 1 peripher, 1 timer/counter 1 contro, 2 timer/counter 1 peripheral registers -5 – Maxim Integrated MAXQ Family User Manual

Page 76: 1 timer/counter 1 control register (t1cn) -5, Maxq family user’s guide, 2 timer/counter 1 peripheral registers, 1 timer/counter 1 control register (t1cn)

(T1CN.2) must also be set to logic 1 to enable the timer. The DCEN bit has no effect in this mode. This mode produces a 50% duty

cycle square-wave output. The frequency of the square wave is given by the formula in Figure 8-4. Each timer overflow causes an edge

transition on the pin, i.e., the state of the pin toggles. Note that the timer itself does not generate an interrupt, but if needed, the Timer

1 external interrupt is still available for use when enabled (EXEN1 = 1).

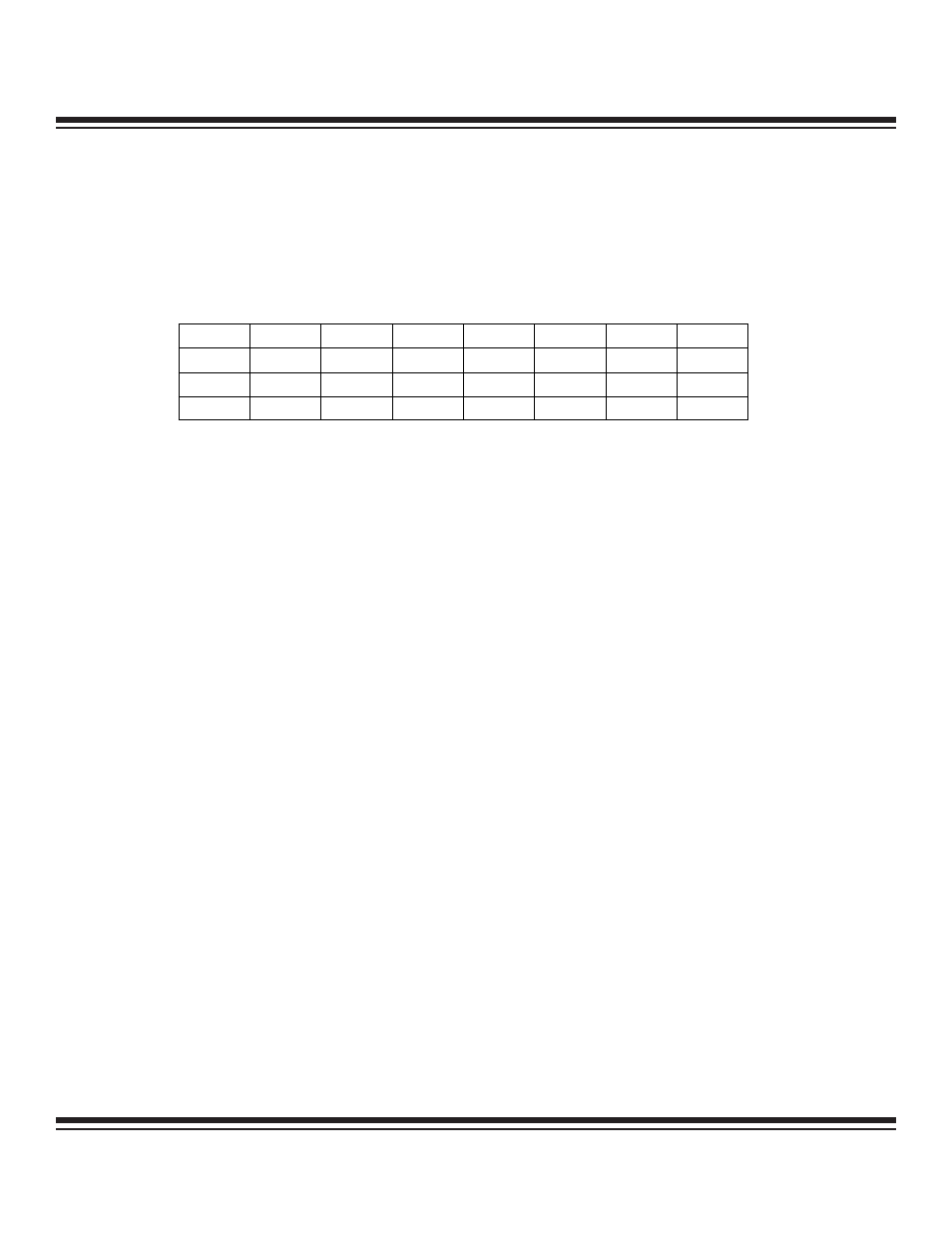

8.2 Timer/Counter 1 Peripheral Registers

8.2.1 Timer/Counter 1 Control Register (T1CN)

Bit 7: Timer 1 Overflow Flag (TF1). This bit is set when Timer 1 overflows from FFFFh or the count is equal to the capture register in

down count mode. It must be cleared by software.

Bit 6: External Timer 1 Trigger Flag (EXF1). A negative transition on the T1EX causes this flag to be set if (CP/RL1 = EXEN1 = 1) or

(CP/RL1 = DCEN = 0 and EXEN1 = 1). When CP/RL1 = 0 and DCEN = 1, EXF1 toggles whenever Timer 1 underflows or overflows. In

this mode, EXF1 can be used as the 17th Timer bit and will not cause an interrupt. If set by a negative transition, this flag must be

cleared by software. Setting this bit to 1 forces a Timer interrupt if enabled.

Bit 5: Timer 1 Output Enable (T1OE). Setting this bit to 1 enables the clock output function of T1 pin if C/T1 = 0. Timer 1 rollovers will

not cause interrupts. Clearing this bit to 0 causes the T1 pin to function as either a standard port pin or a counter input for Timer 1.

Bit 4: Down Count Enable (DCEN). This bit, in conjunction with the T1EX pin, controls the direction that Timer 1 counts in 16-bit auto-

reload mode. Clearing this bit to 0 causes Timer 1 to count up. Setting this bit to 1 causes Timer 1 to count up if the T1EX pin is 1 and

to count down if the T1EX pin is 0.

Bit 3: Timer 1 External Enable (EXEN1). Setting this bit to 1 enables the capture/reload function on the T1EX pin for a negative tran-

sition. Clearing this bit to 0 causes Timer 1 to ignore all external events on T1EX pin.

Bit 2: Timer 1 Run Control (TR1). Setting this bit enables Timer 1. Clearing this bit halts the Timer 1.

Bit 1: Counter/Timer Select (C/

T1). This bit determines whether Timer 1 functions as a Timer or counter. Setting this bit to 1 causes

Timer 1 to count negative transitions on the T1 pin. Clearing this bit to 0 causes Timer 1 to function as a Timer. The speed of Timer 1

is determined by the T1M bit, either divide by 1 or divide by 12 of the system clock, including the clock output mode.

Bit 0: Capture/Reload Select (CP/

RL1). This bit determines whether the capture or reload function is used for Timer 1. Timer 1 func-

tions in an auto-reload mode following each overflow. Setting this bit to 1 causes a Timer 1 capture to occur when a falling edge is

detected on T1EX if EXEN1 = 1. Clearing this bit to 0 causes an auto-reload to occur when Timer 1 overflow or a falling edge is detect-

ed on T1EX if EXEN1 = 1.

8-5

MAXQ Family User’s Guide

Bit #

7

6

5

4

3

2

1

0

Name

TF1

EXF1

T1OE

DCEN

EXEN1

TR1

C/T1

CP/RL1

Reset

0

0

0

0

0

0

0

0

Access

rw

rw

rw

rw

rw

rw

rw

rw

r = read, w = write

Maxim Integrated