3 breakpoint 2 regist, 4 breakpoint 3 regist, 3 breakpoint 2 register (bp2) -6 – Maxim Integrated MAXQ Family User Manual

Page 164: 4 breakpoint 3 register (bp3) -6, Maxq family user’s guide

16-6

MAXQ Family User’s Guide

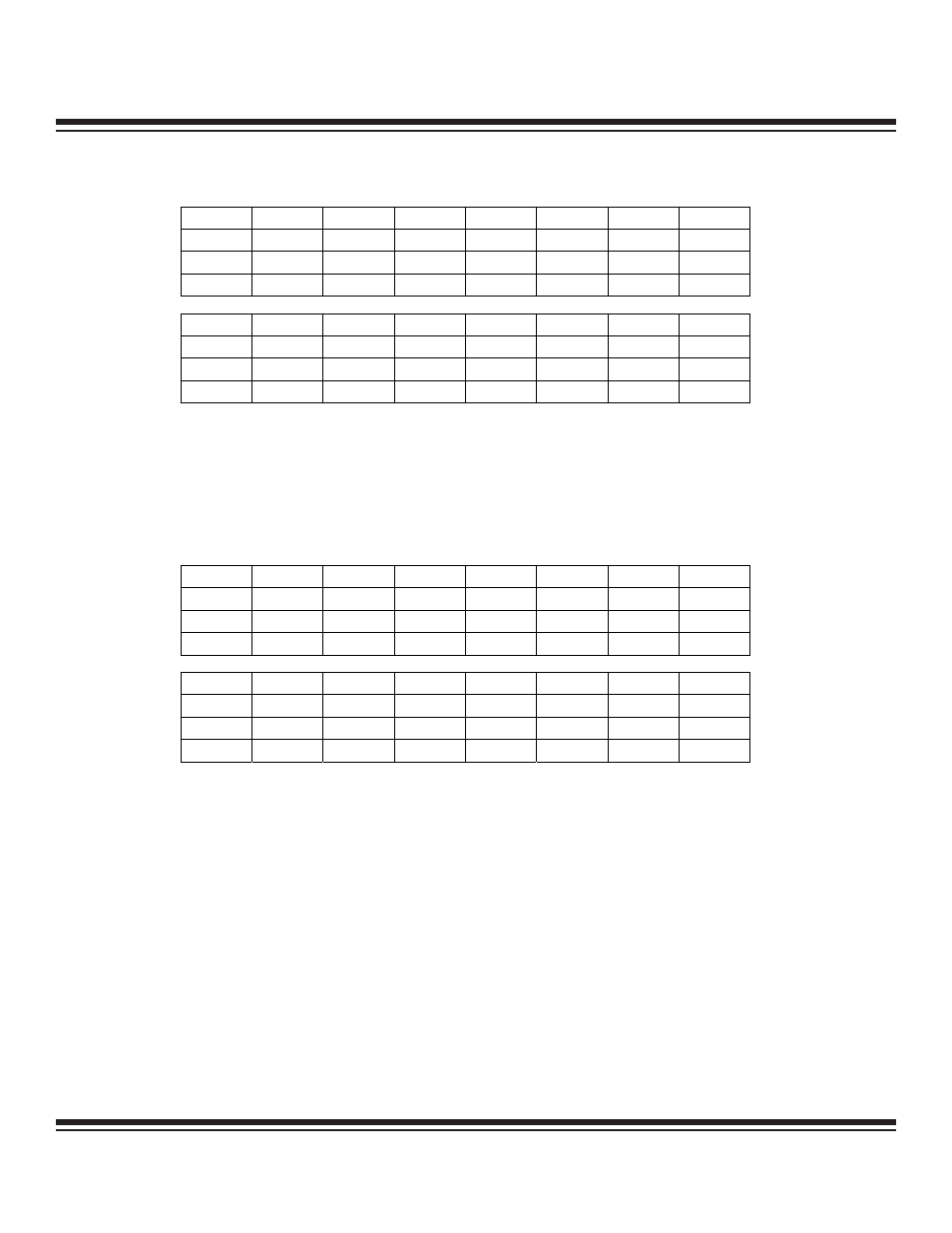

16.1.1.3 Breakpoint 2 Register (BP2)

Bits 15 to 0: Breakpoint 2 (BP2.[15:0]). This register is accessible only via background mode read/write commands. Breakpoint reg-

isters BP0, BP1, BP2, and BP3 serve as program memory address breakpoints. When DME bit is set in background mode, the debug

engine monitors the program-address bus activity while the CPU is executing the user program. If an address match is detected, a

break occurs, allowing the debug engine to take control of the CPU and enter debug mode.

16.1.1.4 Breakpoint 3 Register (BP3)

Bits 15 to 0: Breakpoint 3 (BP3.[15:0]). This register is accessible only via background mode read/write commands. Breakpoint reg-

isters BP0, BP1, BP2, and BP3 serve as program memory address breakpoints. When DME bit is set in background mode, the debug

engine monitors the program-address bus activity while the CPU is executing the user program. If an address match is detected, a

break occurs, allowing the debug engine to take control of the CPU and enter debug mode.

Bit #

15

14

13

12

11

10

9

8

Name

BP2.15

BP2.14

BP2.13

BP2.12

BP2.11

BP2.10

BP2.9

BP2.8

Reset

1

1

1

1

1

1

1

1

Access

s

s

s

s

s

s

s

s

Bit #

7

6

5

4

3

2

1

0

Name

BP2.7

BP2.6

BP2.5

BP2.4

BP2.3

BP2.2

BP2.1

BP2.0

Reset

1

1

1

1

1

1

1

1

Access

s

s

s

s

s

s

s

S

s = special

Bit #

15

14

13

12

11

10

9

8

Name

BP3.15

BP3.14

BP3.13

BP3.12

BP3.11

BP3.10

BP3.9

BP3.8

Reset

1

1

1

1

1

1

1

1

Access

s

s

s

s

s

s

s

s

Bit #

7

6

5

4

3

2

1

0

Name

BP3.7

BP3.6

BP3.5

BP3.4

BP3.3

BP3.2

BP3.1

BP3.0

Reset

1

1

1

1

1

1

1

1

Access

s

s

s

s

s

s

s

S

s = special

Maxim Integrated