Standard event status, 2 standard event status – GW Instek APS-1102A User Manual User Manual

Page 236

APS-1102A User Manual

APS-1102A

6-52

6.5.2 Standard event status

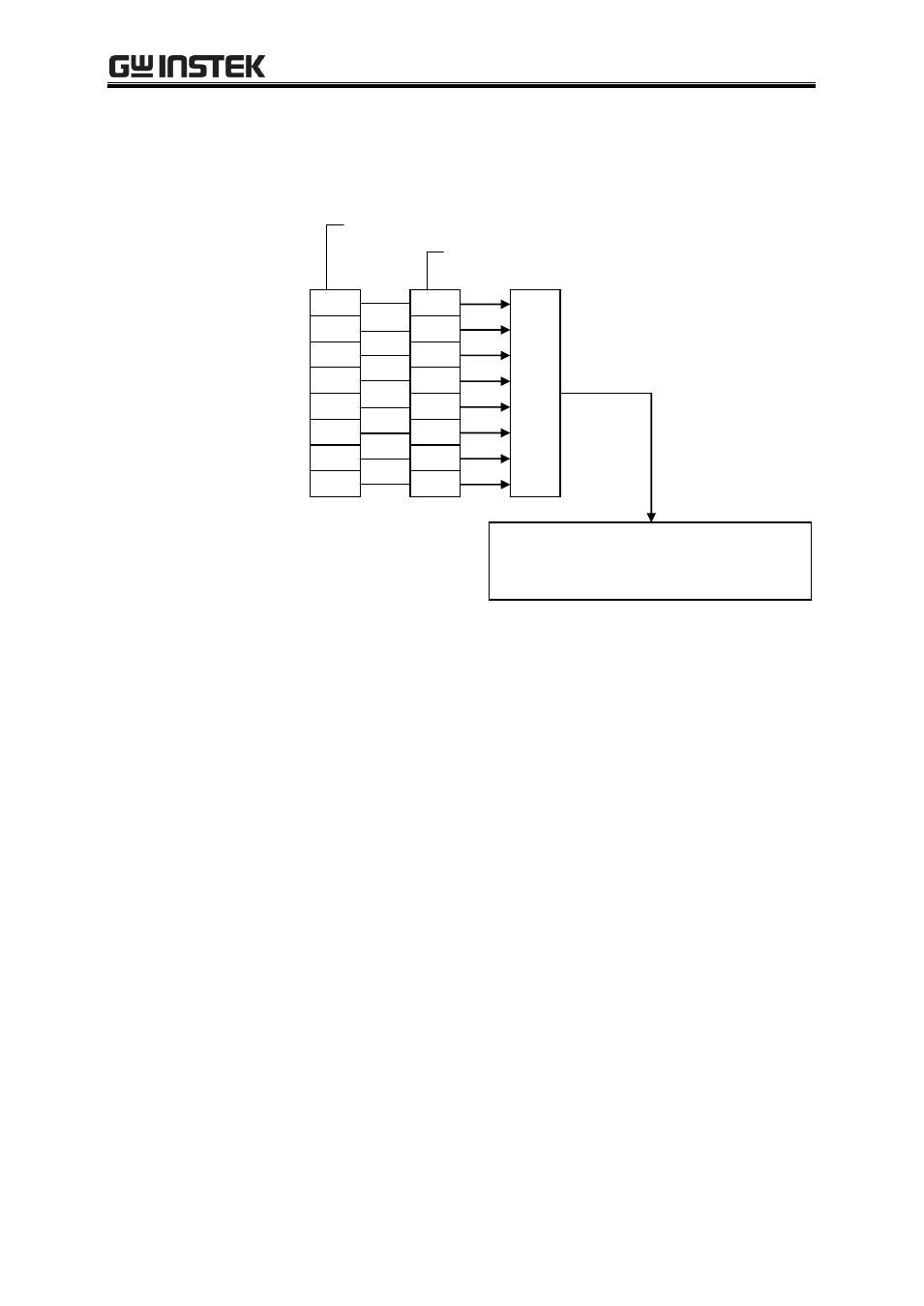

The structure of the standard event status register is shown in Figure 6-5 below.

Power on (PON)

User request (URQ)

Command error (CME)

Execution error (EXE)

Device specific error (DDE)

Query error (QYE)

Request control (RQC)

Operation complete (OPC)

7

6

5

4

3

2

1

0

ESR (standard event register)

7

6

5

4

3

2

1

0

L

o

g

ic

a

l OR

ESE (standard event enable register)

Standard event status summary

Status byte (bit 5)

Figure 6-5. Standard Event Status Register

The definition of the standard event status register is listed in Table6-15. Bits in the standard event status

register become valid when 1 is set to the standard event status enable register, and the ORed result of the

valid bits is reflected in the ESB bit of the status bit register.

The standard event status register can be read by an

ESR? query.

All of the bits are cleared when they are read by an *ESR? query, when a *CLS command is executed, or

when the power is turned on again (except that the PON bit is set to 1 when the power is turned on again).

- GDB-03 (99 pages)

- GLA-1000 Series User Manual (111 pages)

- GLA-1000 Series Quick start guide (20 pages)

- GOS-630FC (20 pages)

- GOS-635G (36 pages)

- GOS-6000 Series (27 pages)

- GOS-6103C (30 pages)

- GOS-6100 Series (30 pages)

- GRS-6000A Series (51 pages)

- GDS-122 Installation Guide (4 pages)

- GDS-122 User Manual (52 pages)

- GDS-2000A series CAN/LIN bus User Manual (18 pages)

- GDS-2000A series Quick start guide for DS2-FGN (6 pages)

- GDS-2000A series Freewave User Manual (26 pages)

- GDS-2000A series Quick start guide for Logic analyzer option (18 pages)

- GDS-2000A series Quick start quide for DS2-LAN (2 pages)

- GDS-2000A series Option User Manual (80 pages)

- GDS-2000A series User Manual (261 pages)

- GDS-2000A series Programming Manual (272 pages)

- GDS-2000A series Single sheet for LA Quick start guide (2 pages)

- GBS-1000 Series Programming Manual (88 pages)

- GBS-1000 Series User Manual (187 pages)

- GDS-1000-U Series firmware upgrade (1 page)

- GDS-1000-U Series Programming Manual (70 pages)

- GDS-1000-U Series Quick start guide (2 pages)

- GDS-1000-U Series User Manual (133 pages)

- GDS-1000A-U Series Programming Manual (88 pages)

- GDS-1000A-U Series Quick start guide (2 pages)

- GDS-1000A-U Series User Manual (148 pages)

- GDS-3000 Series GCP-530/1030 current probe User Manual (40 pages)

- GDS-3000 Series GDP-025/050/100 differential probe User Manual (21 pages)

- GDS-3000 Series DS3-PWR Power analysis manual (37 pages)

- GDS-3000 Series User Manual (209 pages)

- GDS-3000 Series Programming Manual (103 pages)

- GDS-3000 Series DS3-SBD Serial Bus decode (29 pages)

- GDS-3000 Series GKT-100 deskew fixture User Manual (1 page)

- GDS-3000 Series GUG-001, GPIB to USB adapter User Manual (15 pages)

- GDS-300 Series User Manual (188 pages)

- GDS-300 Series Programming Manual (139 pages)

- GDS-300 Series Quick start guide (21 pages)

- GRF-3300 Series Student Manual (26 pages)

- GRF-3300 Series Teacher Manual (26 pages)

- GRF-1300A (124 pages)

- GSP-810 User Manual (40 pages)

- GSP-810 Software Manual (3 pages)