6 scsi bus interface signals, Table 3.7 scsi bus interface signals, Scsi bus interface signals – Avago Technologies LSI53C825AE User Manual

Page 80

3-10

Signal Descriptions

3.1.6 SCSI Bus Interface Signals

describes the SCSI Bus Interface Signals group:

Table 3.7

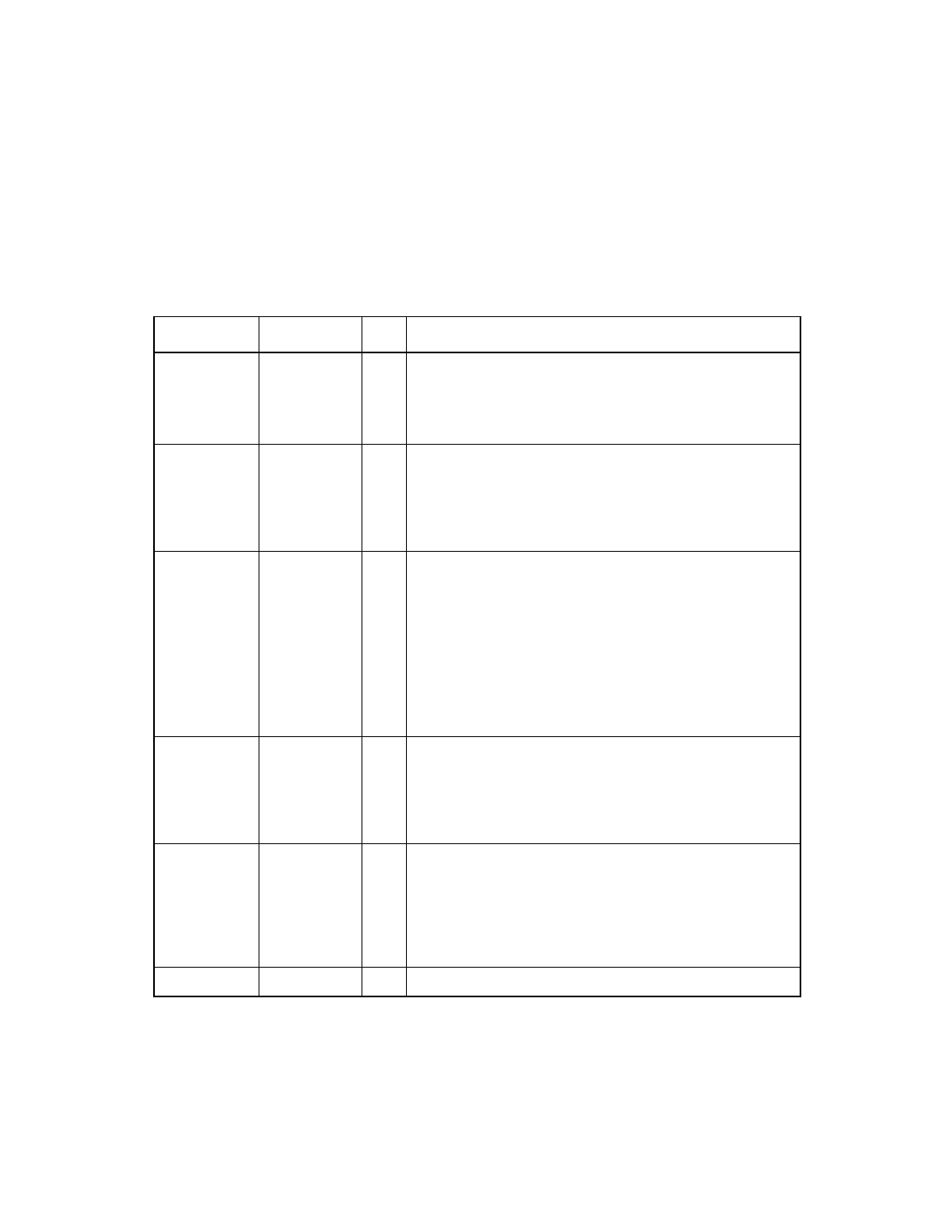

SCSI Bus Interface Signals

Name

Pin No.

Type Description

SCLK

56

I

SCLK is used to derive all SCSI-related timings. The speed

of this clock is determined by the application’s requirements;

in some applications SCLK may be sourced internally from

the PCI bus clock (CLK). If SCLK is internally sourced, then

the SCLK pin should be tied LOW.

SD[15:0]/,

SDP[1:0]/

113, 115, 116,

117, 85, 86,

87, 89, 102,

103, 105, 106,

107, 108, 110,

111, 112, 101

I/O

SCSI Data includes the following data lines and parity

signals: SD[15:0]/ (16-bit SCSI data bus), and SDP[1:0]/

(SCSI data parity bits).

SCTRL/

92, 90, 95, 91,

97, 98, 100,

96, 94

I/O

SCSI Control includes the following signals:

SC_D/

SCSI phase line, command/data

SI_O/

SCSI phase line, input/output

SMSG/

SCSI phase line, message

SREQ/

Data handshake signal from target device

SACK/

Data handshake signal from initiator device

SBSY/

SCSI bus arbitration signal, busy

SATN/

SCSI Attention, the initiator is requesting a

message out phase

SRST/

SCSI bus reset

SSEL/

SCSI bus arbitration signal, select device

SDIR[15:0]

131, 132, 134,

135, 80, 81,

82, 83, 120,

121, 122, 124,

125, 126, 127,

129

O

Driver direction control for SCSI data lines.

SDIRP[1:0]

(SDIPR1 not

available on

LSI53C825AJ)

130, 119

O

Driver direction control for SCSI parity signals. In the

LSI53C825AJ, this pin is replaced by the TCK JTAG signal. If

the device is used in a wide differential system, use the

SDIRP0 pin to control the direction of the differential

transceiver for both the SP0 and SP1 signals. The SDIRP0

signal is capable of driving both direction inputs from a

transceiver.

SELDIR

76

O

Driver Enable Control for SCSI SEL/ signal.