2 address and data signals, Table 3.3 address and data signals, Address and data signals – Avago Technologies LSI53C825AE User Manual

Page 77: Address and, Data signals

PCI Bus Interface Signals

3-7

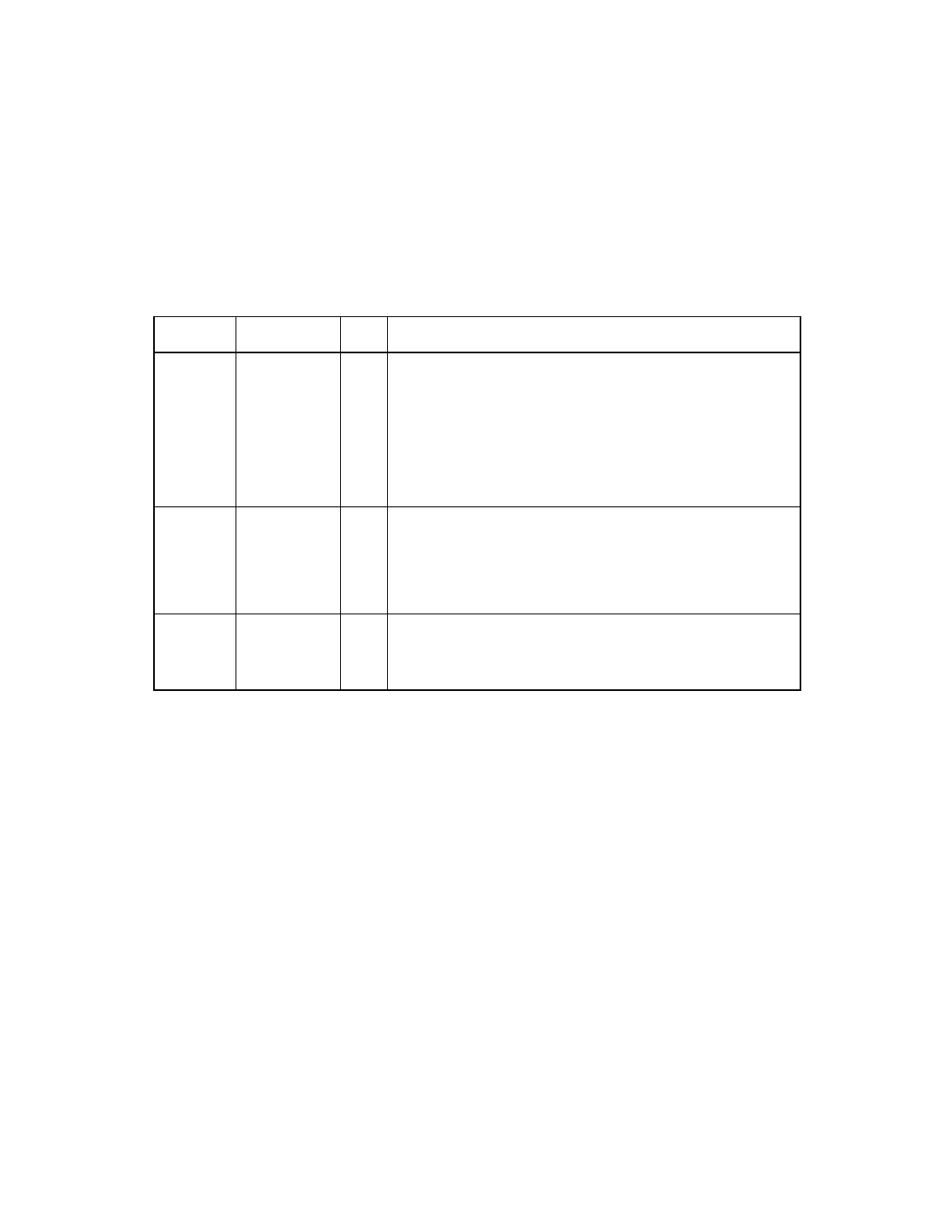

3.1.2 Address and Data Signals

describes the signals for the Address and Data Signals group:

Table 3.3

Address and Data Signals

Name

Pin No.

Type

Description

AD[31:0]

150, 151, 153,

154, 156, 157,

159, 160, 3, 5,

6, 7, 9, 11, 12,

13, 28, 29, 30,

32, 34, 35, 36,

38, 40, 41, 43,

44, 46, 47, 49,

50

T/S

Physical longword Address and Data are multiplexed on the

same PCI pins. During the first clock of a transaction,

AD[31:0] contain a physical address. During subsequent clocks,

AD[31:0] contain data. A bus transaction consists of an address

phase, followed by one or more data phases. PCI supports both

read and write bursts. AD[7:0] define the least significant byte,

and AD[31:24] define the most significant byte.

C_BE[3:0]/

1, 15, 26, 39

T/S

Bus Command and Byte Enables are multiplexed on the same

PCI pins. During the address phase of a transaction,

C_BE[3:0]/ define the bus command. During the data phase,

C_BE[3:0]/ are used as byte enables. The byte enables

determine which byte lanes carry meaningful data. C_BE(0)/

applies to byte 0, and C_BE(3)/ to byte 3.

PAR

25

T/S

Parity is the even parity bit that protects the AD[31:0] and

C_BE[3:0]/ lines. During address phase, both the address and

command bits are covered. During data phase, both data and

byte enables are covered.