Avago Technologies LSI53C825AE User Manual

Page 168

4-80

Registers

Wide Residue message is received. It may also be an

overrun data byte. The power-up value of this register is

indeterminate.

Register: 0x46 (0xC6)

Memory Access Control (MACNTL)

Read/Write

TYP[3:0]

Chip Type

[7:4]

These bits identify the chip type for software purposes.

This technical manual applies to devices that have these

bits set to 0x06.

Bits 3 through 0 of this register are used to determine if

an external bus master access is to local or far memory.

When bits 3 through 0 are set, the corresponding access

is considered local and the MAC/_TESTOUT pin is driven

high. When these bits are clear, the corresponding

access is to far memory and the MAC/_TESTOUT pin is

driven low. This function is enabled after a Transfer

Control SCRIPTS instruction is executed.

DWR

DataWR

3

This bit is used to define if a data write is considered

local memory access.

DRD

DataRD

2

This bit is used to define if data write is considered local

memory access.

PSCPT

Pointer SCRIPTS

1

This bit is used to define if a pointer to a SCRIPTS

indirect or table indirect fetch is considered local memory

access.

SCPTS

SCRIPTS

0

This bit is used to define if a SCRIPTS fetch is

considered local memory access.

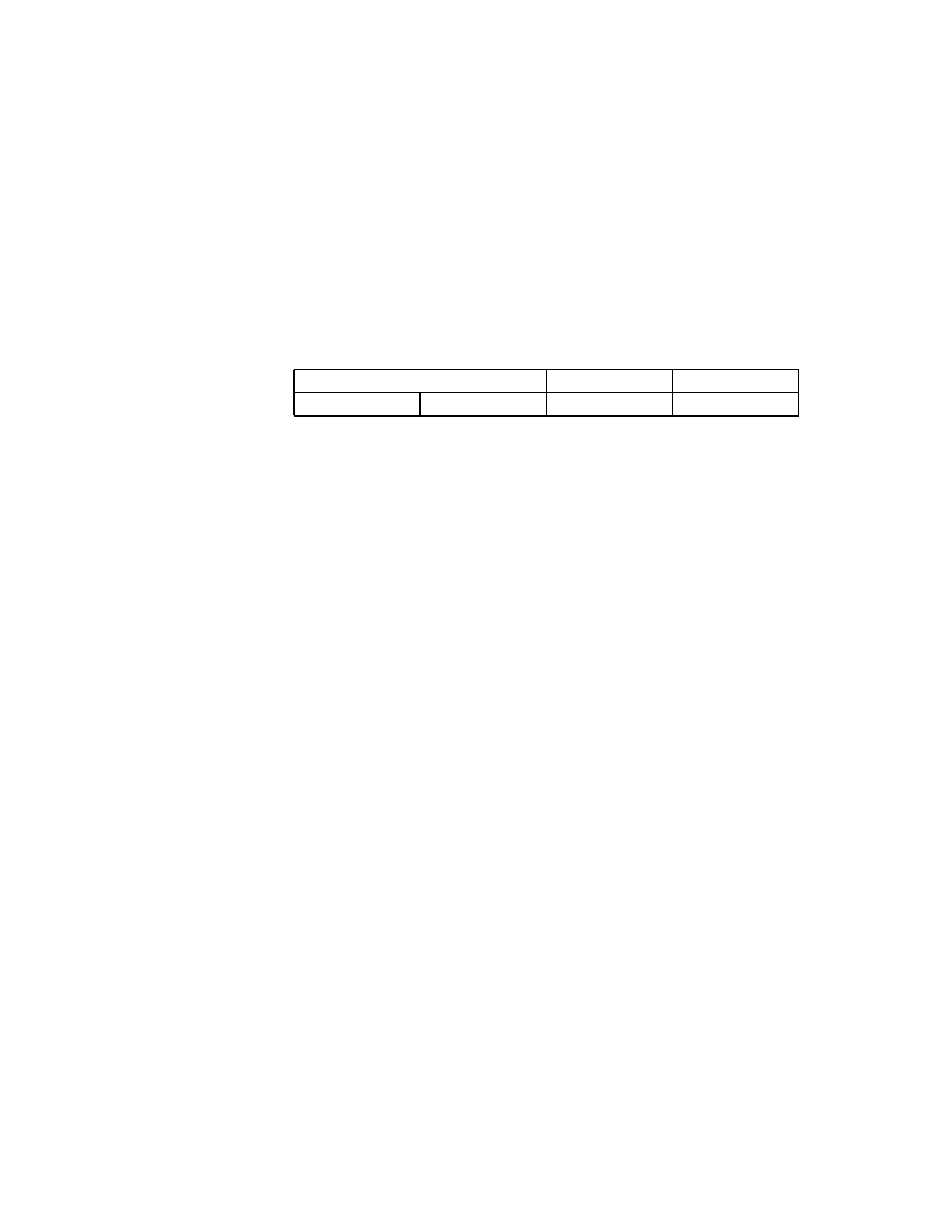

7

4

3

2

1

0

TYP[3:0]

DWR

DRD

PSCPT

SCPTS

0

1

1

0

0

0

0

0