Table 2.5 scsi parity errors and interrupts, 8 dma fifo, Figure2.1 dma fifo sections – Avago Technologies LSI53C825AE User Manual

Page 47: Table 2.5

PCI Cache Mode

2-23

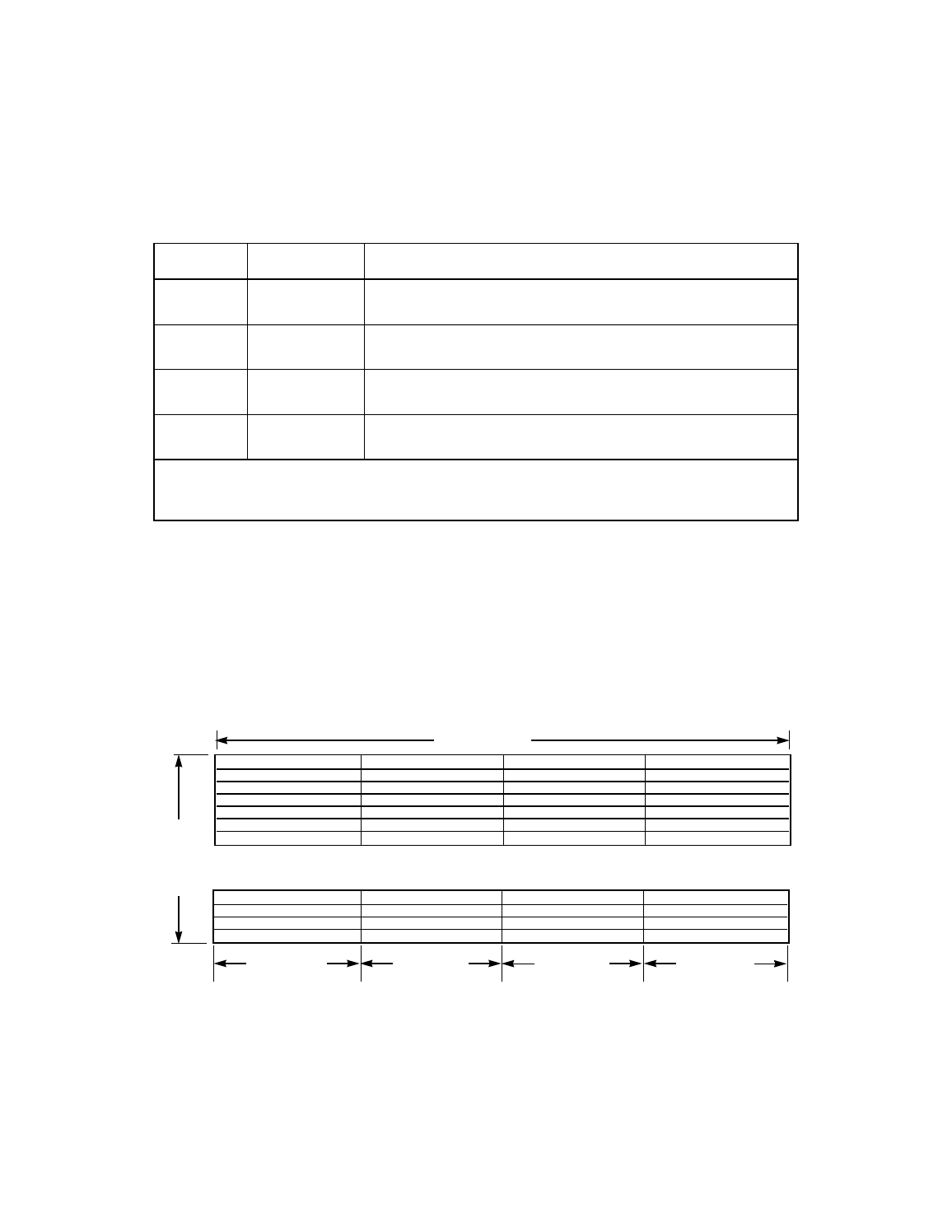

2.4.8 DMA FIFO

The DMA FIFO is 4 bytes wide by 134 transfers deep. The DMA FIFO is

illustrated in

. To assure compatibility with older products in the

LSI53C8XX family, the user may set the DMA FIFO size to 88 bytes by

clearing the DMA FIFO Size bit, bit 5 in the

register.

Figure 2.1

DMA FIFO Sections

Table 2.5

SCSI Parity Errors and Interrupts

DPH

PAR

Description

0

0

Halts when a parity error occurs in target or initiator mode and will

not generate an interrupt.

0

1

Halts when a parity error occurs in target mode and will generate

an interrupt in target or initiator mode.

1

0

Does not halt in target mode when a parity error occurs until the

end of the transfer. An interrupt will not be generated.

1

1

Does not halt in target mode when a parity error occurs until the

end of the transfer. An interrupt will be generated.

Key:

DHP = Disable Halt on SATN/ or Parity Error (bit 5,

.

PAR = Parity Error (bit 0,

SCSI Interrupt Enable Zero (SIEN0)

134

Transfers

Deep

.

.

.

.

.

.

32 Bytes Wide

8 Bits

Byte Lane 3

8 Bits

Byte Lane 2

8 Bits

Byte Lane 1

8 Bits

Byte Lane 0