Table 2.4 scsi parity control, Table 2.4 – Avago Technologies LSI53C825AE User Manual

Page 46

2-22

Functional Description

Status of SCSI Parity

Signal

, Bit 0

This status bit represents the active HIGH current state

of the SCSI SDP0 parity signal.

SCSI SDP1 Signal

, Bit 0

This bit represents the active HIGH current state of the

SCSI SDP1 parity signal.

Latched SCSI Parity

, Bit 3

and

,

Bit 3

These bits reflect the SCSI odd parity signal

corresponding to the data latched into the

register.

Master Parity Error

Enable

, Bit 3

Enables parity checking during master data phases.

Master Data Parity Error

, Bit 6

Set when the LSI53C825A as a master detects that a

target device has signaled a parity error during a data

phase.

Master Data Parity Error

Interrupt Enable

Bit 6

By clearing this bit, a Master Data Parity Error will not

cause IRQ/ to be asserted, but the status bit will be set

in the

register.

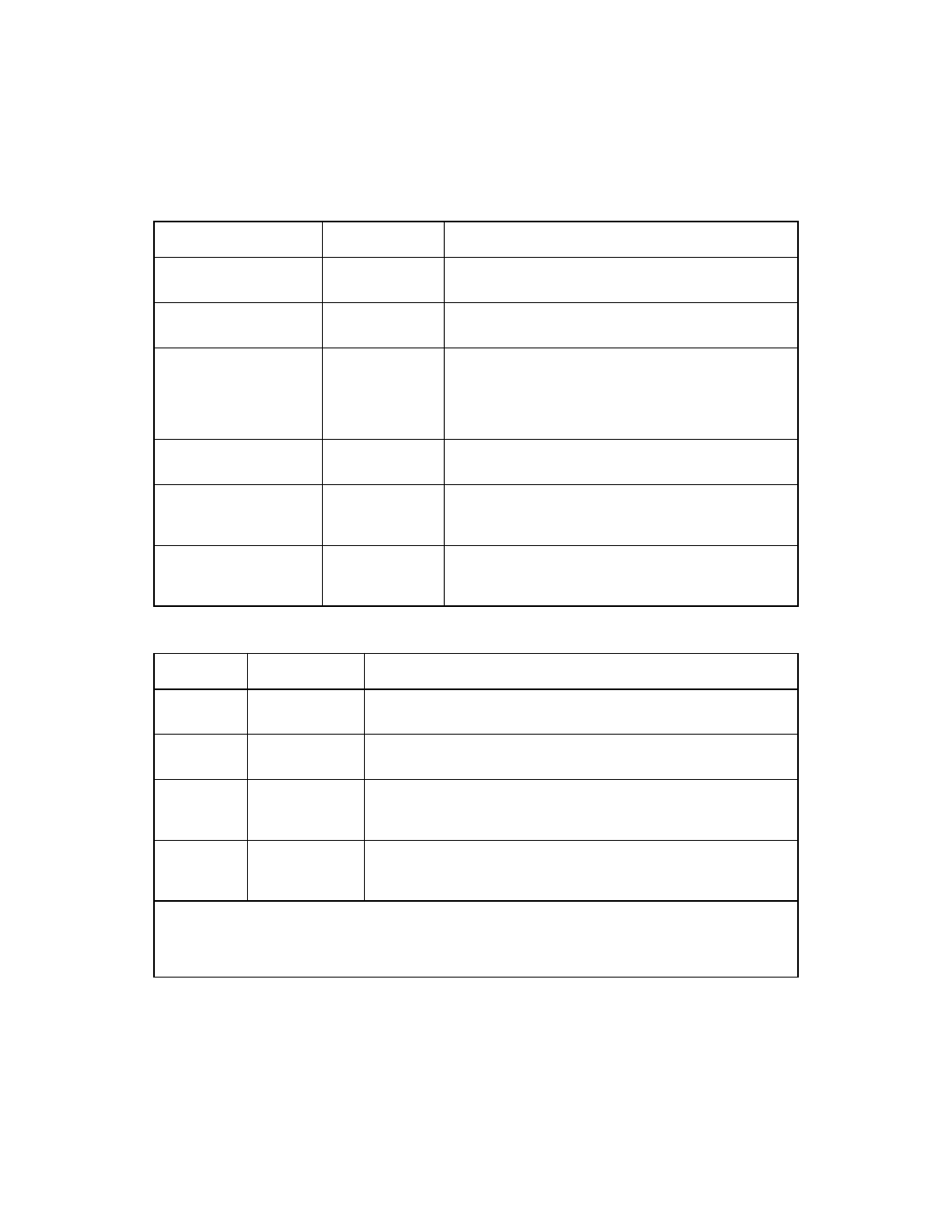

Table 2.4

SCSI Parity Control

EPC

AESP

Description

0

0

Does not check for parity errors. Parity is generated when sending

SCSI data. Asserts odd parity when sending SCSI data.

0

1

Does not check for parity errors. Parity is generated when sending

SCSI data. Asserts even parity when sending SCSI data.

1

0

Checks for odd parity on SCSI data received. Parity is generated

when sending SCSI data. Asserts odd parity when sending SCSI

data.

1

1

Checks for odd parity on SCSI data received. Parity is generated

when sending SCSI data. Asserts even parity when sending SCSI

data.

1. Key:

EPC = Enable Parity Checking (bit 3,

ASEP = Assert SCSI Even Parity (bit 2,

2. This table only applies when the Enable Parity Checking bit is set.

Table 2.3

Bits Used for Parity Control and Generation (Cont.)

BIt Name

Location

Description