Dma command (dcmd), Bit is clear, the, Next address (dnad) – Avago Technologies LSI53C825AE User Manual

Page 151: Dma next address (dnad)

Operating Registers

4-63

Register: 0x27 (0xA7)

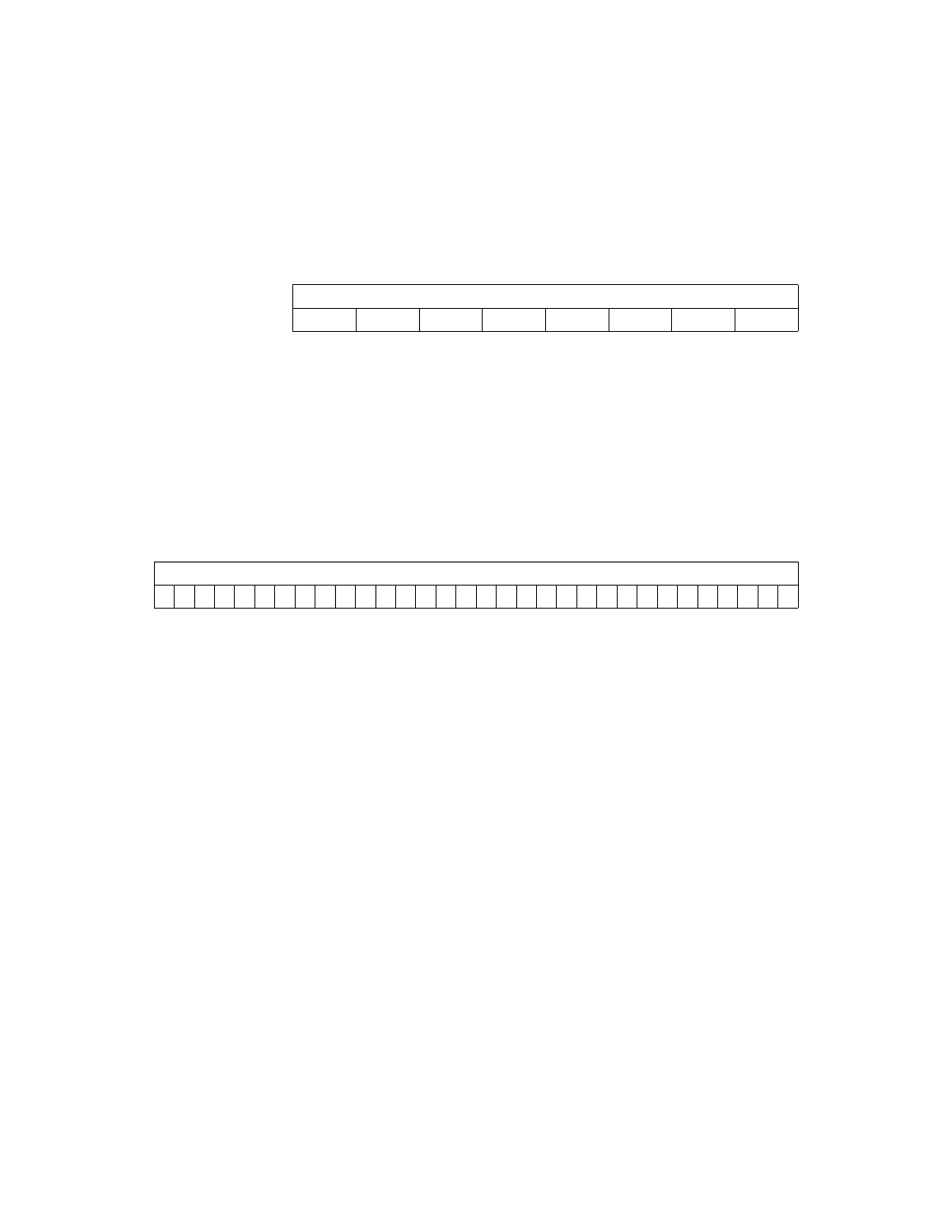

DMA Command (DCMD)

Read/Write

DCMD

DMA Command

[7:0]

This 8-bit register determines the instruction for the

LSI53C825A to execute. This register has a different

format for each instruction. For a complete description

see

Chapter 5, “SCSI SCRIPTS Instruction Set.”

Register: 0x28–0x2B (0xA8–0xAB)

DMA Next Address (DNAD)

Read/Write

DNAD

DMA Next Address

[31:0]

This 32-bit register contains the general purpose address

pointer. At the start of some SCRIPTS operations, its

value is copied from the

register. Its value may not be valid except in

certain abort conditions. The default value of this register

is zero.

This register should not be used to determine data

addresses during a Phase Mismatch interrupt, as its

value is not always correct for this use. The

,

, and

registers should be used to

calculate residual byte counts and addresses as

described in the Data Paths section in

7

0

DCMD

x

x

x

x

x

x

x

x

31

0

DNAD

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0