Altera Video and Image Processing Suite User Manual

Page 89

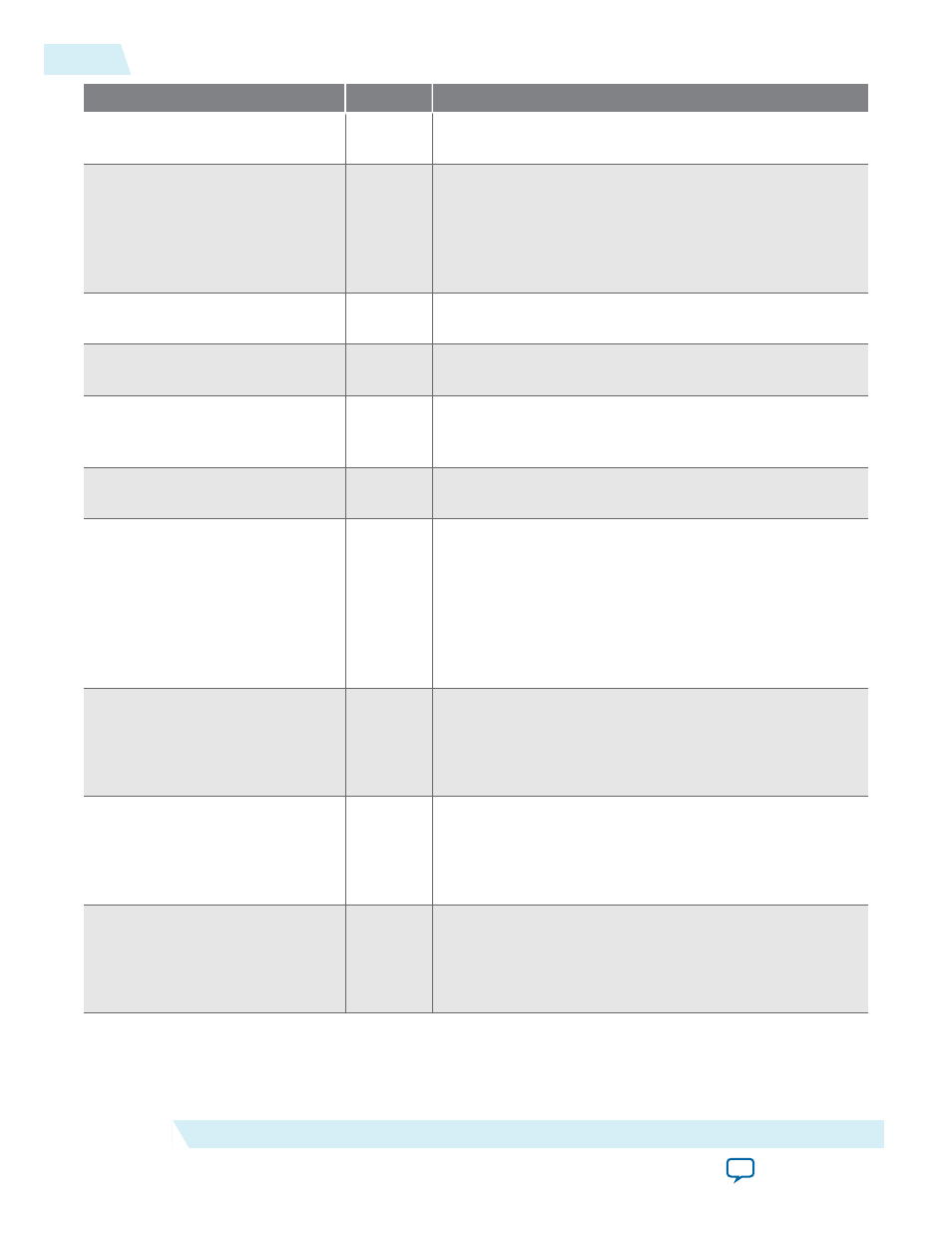

Signal

Direction

Description

dout_valid

Output

dout

port Avalon-ST

valid

signal. This signal is asserted

when the IP core produces data.

status_update_int

Output

control

slave port Avalon-MM interrupt signal. When

asserted, the status registers of the IP core have been

updated and the master must read them to determine

what has occurred.

Note: Present only if you turn on Use control port.

vid_clk

Input

Clocked video clock. All the video input signals are

synchronous to this clock.

vid_data

Input

Clocked video data bus. This bus enables the transfer of

video data into the IP core.

vid_de

Input

This signal is asserted when you turn on Add data enable

signal. This signal indicates the active picture region of an

incoming line.

vid_datavalid

Input

Clocked video data valid signal. Assert this signal when a

valid sample of video data is present on

vid_data

.

vid_locked

Input

Clocked video locked signal. Assert this signal when a

stable video stream is present on the input. Deassert this

signal when the video stream is removed.

CVO II IP core: When 0 this signal is used to reset the

vid_clk

clock domain registers, it is synchronized to the

vid_clk

internally so no external synchronization is

required.

vid_f

Input

Clocked video field signal. For interlaced input, this signal

distinguishes between field 0 and field 1. For progressive

video, you must deassert this signal.

Note: For separate synchronization mode only.

vid_v_sync

Input

Clocked video vertical synchronization signal. Assert this

signal during the vertical synchronization period of the

video stream.

Note: For separate synchronization mode only.

vid_h_sync

Input

Clocked video horizontal synchronization signal. Assert

this signal during the horizontal synchronization period of

the video stream.

Note: For separate synchronization mode only.

4-30

Clocked Video Interface Signals

UG-VIPSUITE

2015.05.04

Altera Corporation

Clocked Video Interface IP Cores