Altera Video and Image Processing Suite User Manual

Page 100

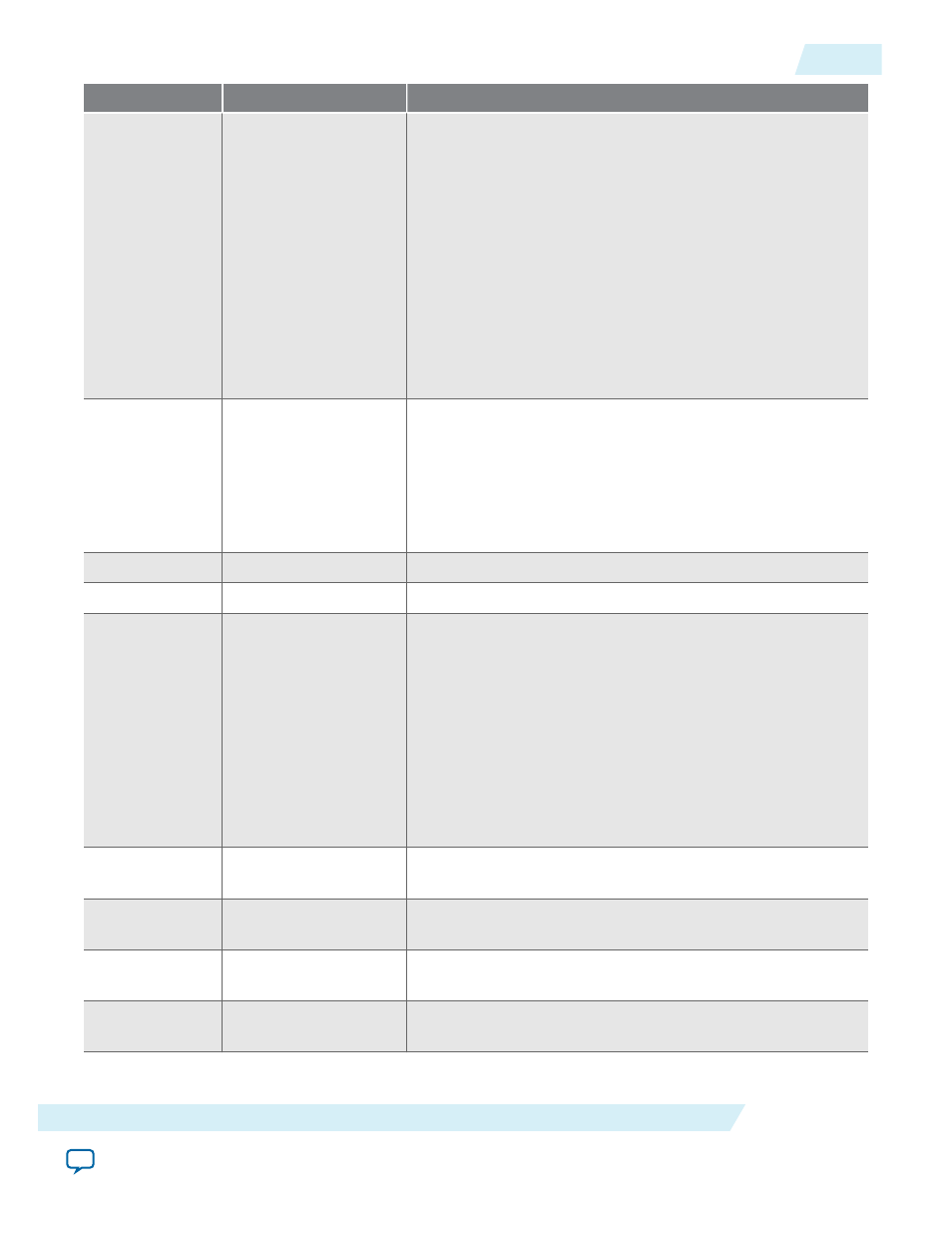

Address

Register

Description

1

Status

• Bit 0 of this register is the

Status

bit.

• This bit is asserted when the CVO IP core is producing

data.

• Bit 1 of the

Status

register is unused.

• Bit 2 is the underflow sticky bit.

• When bit 2 is asserted, the output FIFO has

underflowed. The underflow sticky bit stays asserted

until a 1 is written to this bit.

• Bit 3 is the frame locked bit.

• When bit 3 is asserted, the CVO IP core has aligned its

start of frame to the incoming

sof

signal.

2

Interrupt

Bits 2 and 1 are the interrupt status bits:

• When bit 1 is asserted, the status update interrupt has

triggered.

• When bit 2 is asserted, the locked interrupt has triggered.

• The interrupts stay asserted until a 1 is written to these

bits.

3

Used Words

The used words level of the output FIFO.

4

Video Mode Match

One-hot register that indicates the video mode that is selected.

5

ModeX Control

Video Mode 1 Control.

• Bit 0 of this register is the Interlaced bit:

• Set to 1 for interlaced. Set to 0 for progressive.

• Bit 1 of this register is the sequential output control bit

(only if the Allow output of color planes in sequence

compile-time parameter is enabled).

• Setting bit 1 to 1, enables sequential output from the

CVO IP core (NTSC). Setting bit 1 to a 0, enables

parallel output from the CVO IP core (1080p).

6

Mode1 Sample Count

Video mode 1 sample count. Specifies the active picture width

of the field.

7

Mode1 F0 Line Count

Video mode 1 field 0/progressive line count. Specifies the

active picture height of the field.

8

Mode1 F1 Line Count

Video mode 1 field 1 line count (interlaced video only).

Specifies the active picture height of the field.

9

Mode1 Horizontal

Front Porch

Video mode 1 horizontal front porch. Specifies the length of

the horizontal front porch in samples.

UG-VIPSUITE

2015.05.04

Clocked Video Interface Control Registers

4-41

Clocked Video Interface IP Cores

Altera Corporation