Altera Video and Image Processing Suite User Manual

Page 72

AFD Extractor (Clocked Video Input)

When the output of the CVI IP cores connects to the input of the AFD Extractor, the AFD Extractor

removes any ancillary data packets from the stream and checks the DID and secondary DID (SDID) of the

ancillary packets contained within each ancillary data packet. If the packet is an AFD packet (DID = 0x41,

SDID = 0x5), the extractor places the contents of the ancillary packet into the AFD Extractor register map.

You can get the AFD Extractor from

.

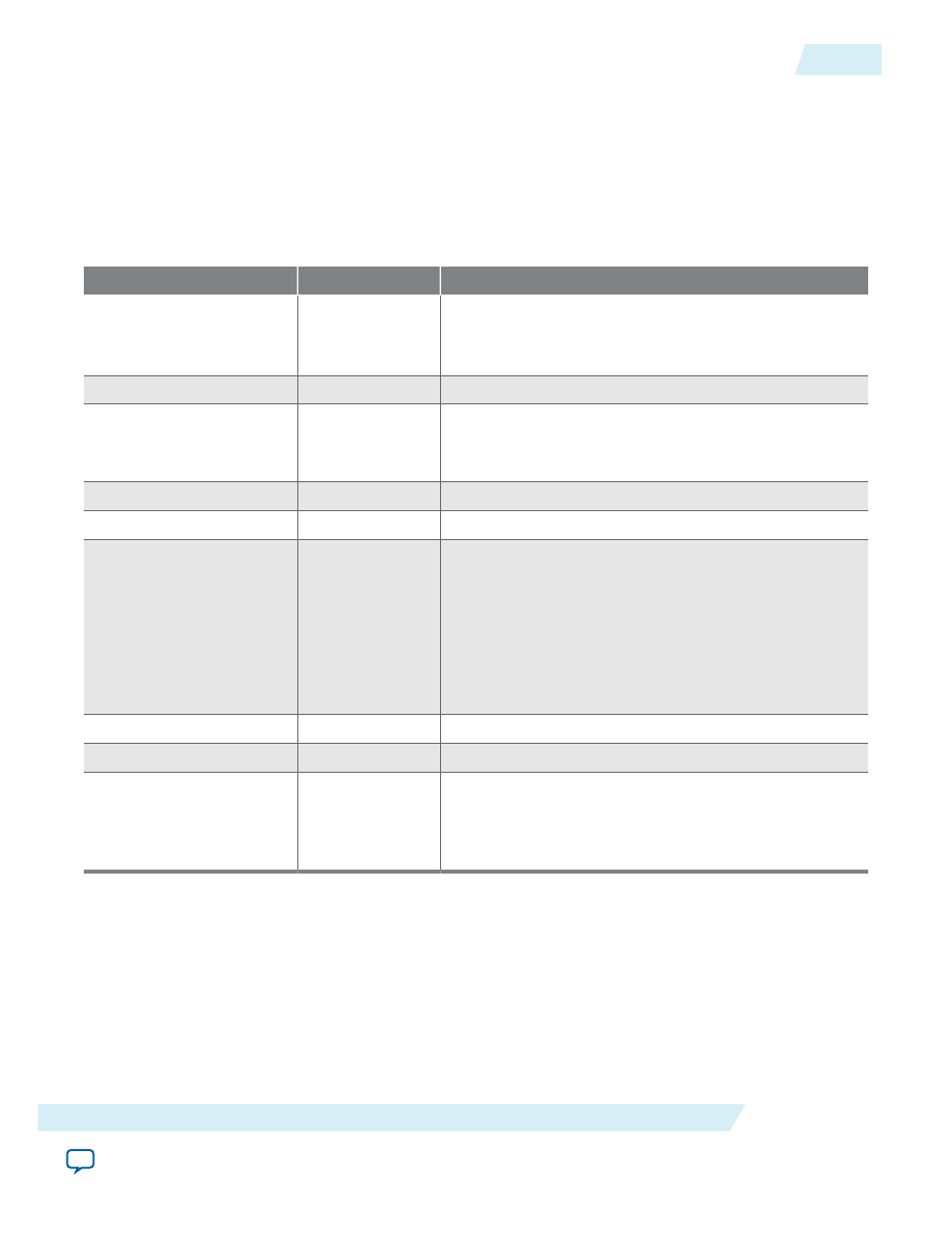

Table 4-7: AFD Extractor Register Map

Address

Register

Description

0

Control

• When bit 0 is 0, the core discards all packets.

• When bit 0 is 1, the core passes through all non-ancillary

packets.

1

—

Reserved.

2

Interrupt

When bit 1 is 1, the core detects a change to the AFD data

and the sets an interrupt. Writing a 1 to bit 1 clears the

interrupt.

3

AFD

Bits 0-3 contain the active format description code.

4

AR

Bit 0 contains the aspect ratio code.

5

Bar data flags

• When AFD is 0000 or 0100, bits 0-3 describe the contents

of bar data value 1 and bar data value 2.

• When AFD is 0011, bar data value 1 is the pixel number

end of the left bar and bar data value 2 is the pixel number

start of the right bar.

• When AFD is 1100, bar data value 1 is the line number

end of top bar and bar data value 2 is the line number

start of bottom bar.

6

Bar data value 1

Bits 0-15 contain bar data value 1

7

Bar data value 2

Bits 0-15 contain bar data value 2

8

AFD valid

• When bit 0 is 0, an AFD packet is not present for each

image packet.

• When bit 0 is 1, an AFD packet is present for each image

packet.

Ancillary Packets (Clocked Video Input II)

When you turn on the Extract Ancillary Packets parameter in embedded sync mode, the CVO IP core

extracts any ancillary packets that are present in the Y channel of the incoming video's vertical blanking.

The ancillary packets are stripped of their TRS code and placed in a RAM. You can access these packets by

reading from the

Ancillary Packet

register. The packets are packed end to end from their Data ID to

their final user word.

The RAM is 16 bits wide—two 8-bit ancillary data words are packed at each address location. The first

word is at bits 0–7 and the second word is at bits 8–15. A word of all 1's indicates that no further ancillary

packets are present and can appear in either the first word position or the second word position.

UG-VIPSUITE

2015.05.04

Handling Ancillary Packets

4-13

Clocked Video Interface IP Cores

Altera Corporation