Scaler ii signals, Scaler ii signals -12 – Altera Video and Image Processing Suite User Manual

Page 233

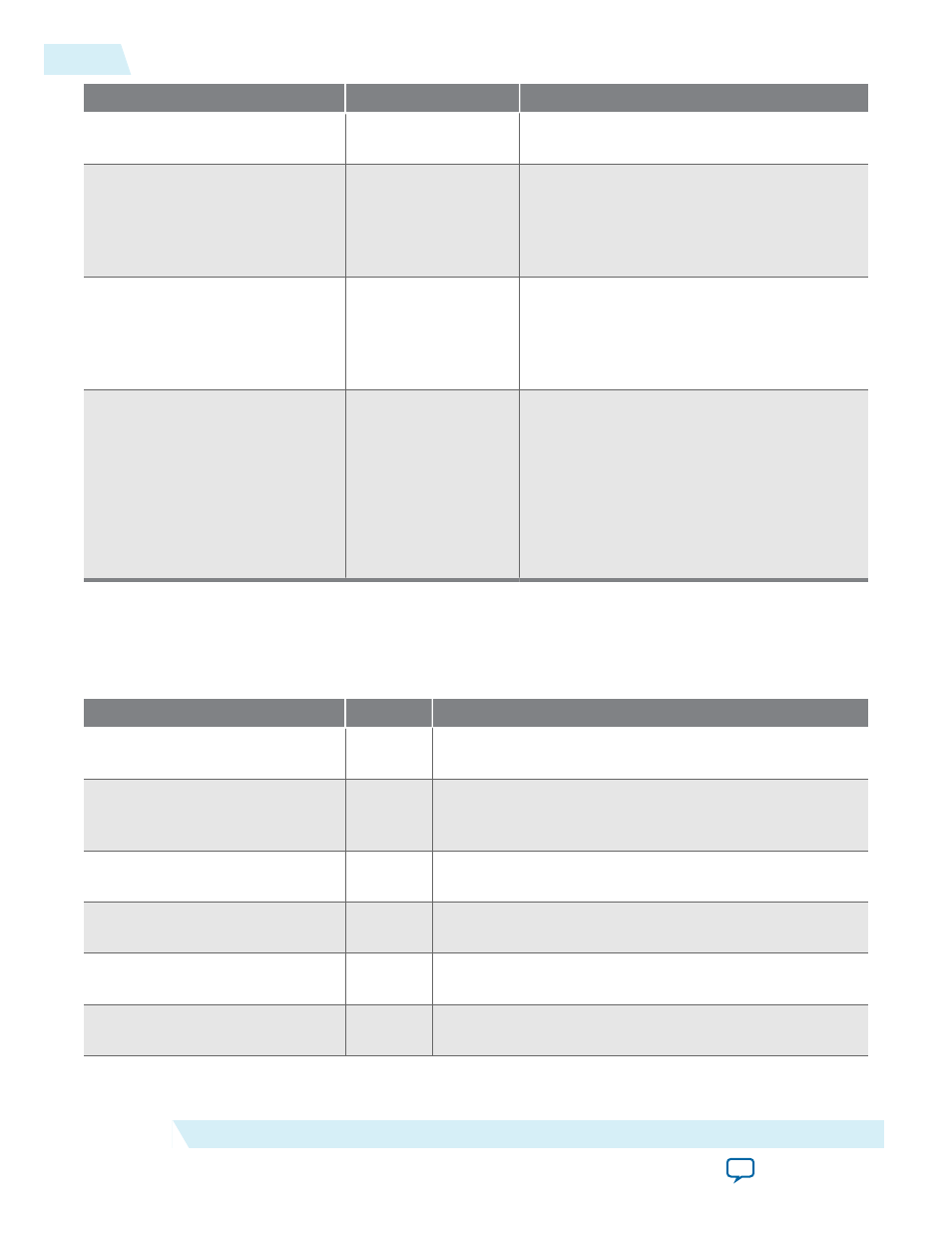

Parameter

Value

Description

Horizontal coefficient banks

1–32, Default = 1

Select the number of banks of horizontal filter

coefficients for polyphase algorithms.

Horizontal coefficient function

• Lanczos_2

• Lanczos_3

• Custom

Select the function used to generate the

horizontal scaling coefficients. Select either

one for the pre-defined Lanczos functions or

choose Custom to use the coefficients saved

in a custom coefficients file.

Horizontal coefficients file

User-specified

When a custom function is selected, you can

browse for a comma-separated value file

containing custom coefficients. Key in the

path for the file that contains these custom

coefficients.

Add extra pipelining registers

On or Off

Turn on to add extra pipeline stage registers

to the data path.

You must to turn on this option to achieve:

• frequency of 150 MHz for Cyclone III or

Cyclone IV devices

• frequencies above 250 MHz for Arria II,

Stratix IV, or Stratix V devices

Scaler II Signals

Table 17-3: Common Signals

Signal

Direction

Description

main_clock

Input

The main system clock. The IP core operates on the rising

edge of this signal.

main_reset

Input

The IP core asynchronously resets when you assert this

signal. You must deassert this signal synchronously to the

rising edge of the

main_clock

signal.

din_data

Input

din

port Avalon-ST

data

bus. This bus enables the

transfer of pixel data into the IP core.

din_endofpacket

Input

din

port Avalon-ST

endofpacket

signal. This signal

marks the end of an Avalon-ST packet.

din_ready

Output

din

port Avalon-ST

ready

signal. This signal indicates

when the IP core is ready to receive data.

din_startofpacket

Input

din

port Avalon-ST

startofpacket

signal. This signal

marks the start of an Avalon-ST packet.

17-12

Scaler II Signals

UG-VIPSUITE

2015.05.04

Altera Corporation

Scaler II IP Core