Avalon-mm master interfaces, Avalon-mm master interfaces -28 – Altera Video and Image Processing Suite User Manual

Page 55

Signal

Width

Direction

waitrequest

1

Output

irq

(6)

1

Output

Note: The list does not include clock and reset signal types. The Video and Image Processing Suite IP

cores do not support Avalon-MM interfaces in multiple clock domains. Instead, the Avalon-MM

slave interfaces must operate synchronously to the main clock and reset signals of the IP core. The

Avalon-MM slave interfaces must operate synchronously to this clock.

The control interfaces of the Video and Image Processing Suite IP cores that do not use a

waitrequest

signal, exhibit the following transfer properties:

• Zero wait states on write operations

• Two wait states on read operation

Avalon-MM Master Interfaces

The Video and Image Processing Suite IP cores use a common type of Avalon-MM master interface for

access to external memory.

Connect these master interfaces to external memory resources through arbitration logic such as that

provided by the system interconnect fabric.

Specification of the Type of Avalon-MM Master Interfaces

The Avalon-MM master interfaces only use certain signals for Video and Image Processing Suite IP cores.

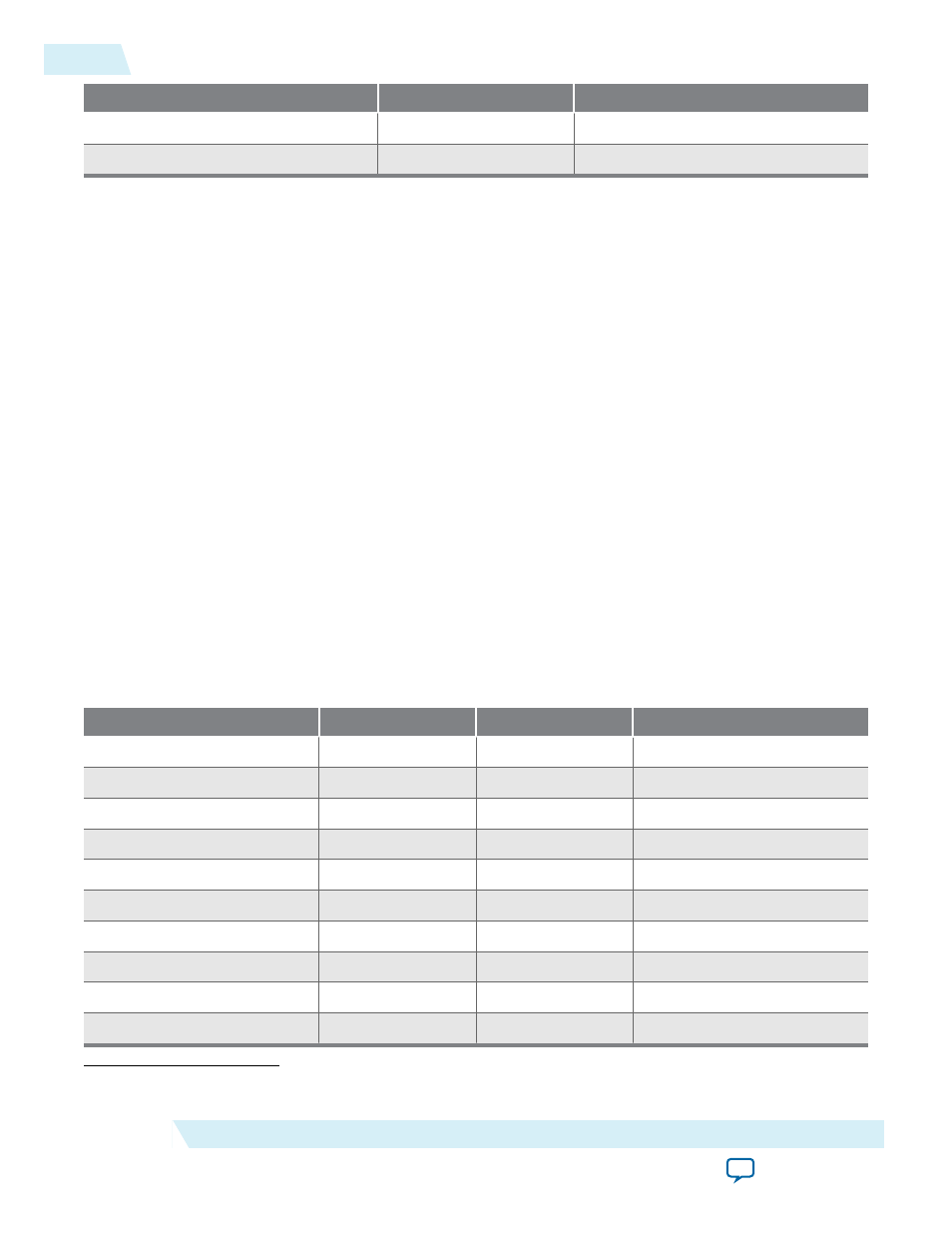

Table 2-13: Avalon-MM Master Interface Signal Types

The table below lists the signals that the Avalon-MM master interfaces use in the Video and Image Processing

Suite IP cores. The unused signals are not listed.

Signal

Width

Direction

Usage

clock

1

Input

Read-Write (optional)

readdata

Variable

Output

Read-only

readdatavalid

1

Read-only

reset

1

Read-Write (optional)

waitrequest

1

Output

Read-Write

address

32

Input

Read-Write

burstcount

Variable

Read-Write

read

1

Input

Read-only

write

1

Input

Write-only

writedata

Variable

Input

Write-only

(6)

For slave interfaces with an interrupt request line.

2-28

Avalon-MM Master Interfaces

UG-VIPSUITE

2015.05.04

Altera Corporation

Interfaces