Control synchronizer control registers, Control synchronizer control registers -6 – Altera Video and Image Processing Suite User Manual

Page 158

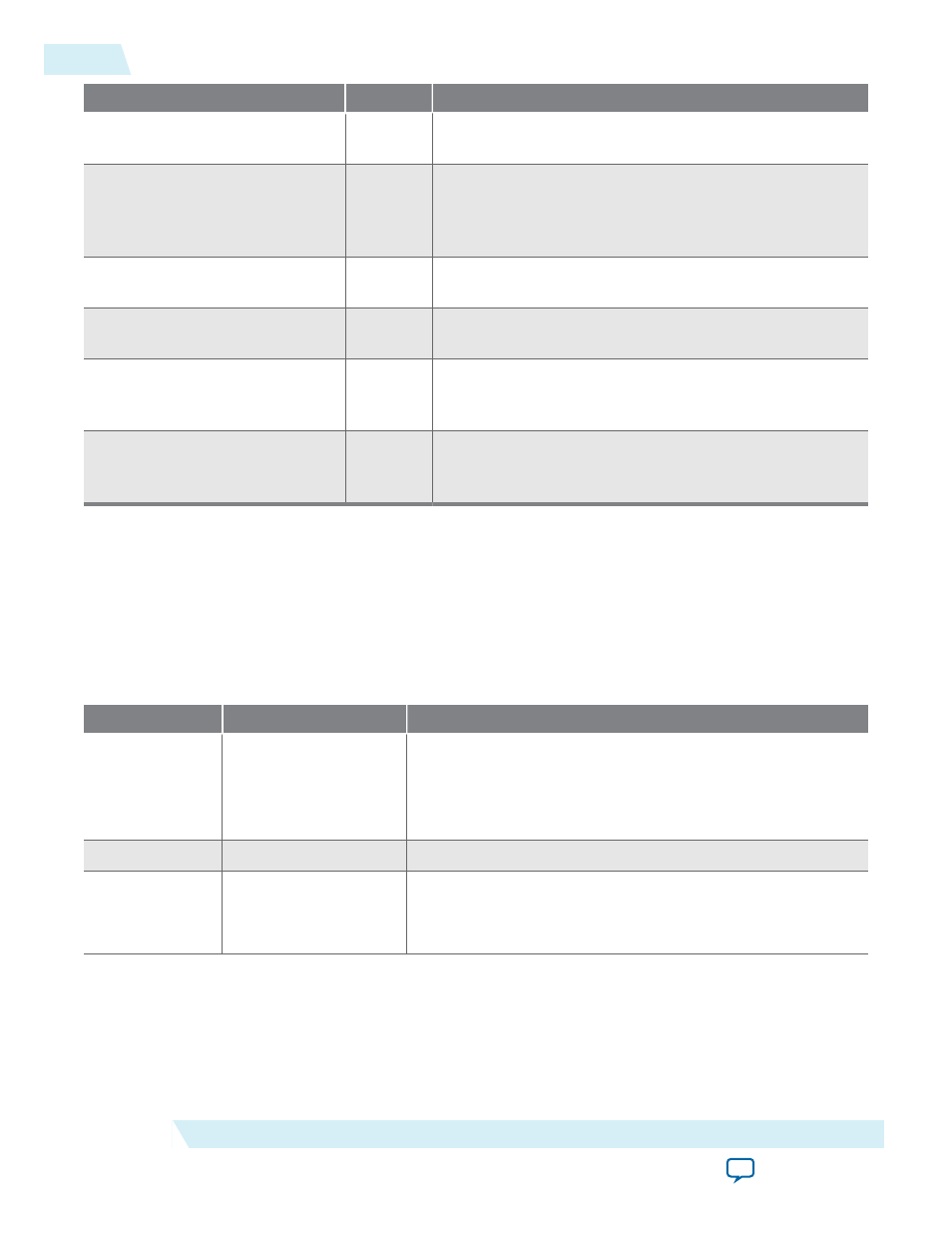

Signal

Direction

Description

slave_av_writedata

Input

slave port Avalon-MM

writedata

bus. The IP core uses

these input lines for write transfers.

status_update_int_w

Output

slave port Avalon-MM

interrupt

signal. Asserted to

indicate that the interrupt registers of the IP core are

updated; and the master must read them to determine

what has occurred.

master_av_address

Output

master port Avalon-MM

address

bus. This bus specifies a

word offset into the Avalon-MM address space.

master_av_writedata

Output

master port Avalon-MM

writedata

bus. The IP core uses

these output lines for write transfers.

master_av_write

Output

master port Avalon-MM

write

signal. Asserted to

indicate write requests from the master to the system

interconnect fabric.

master_av_waitrequest

Input

master port Avalon-MM

waitrequest

signal. The system

interconnect fabric asserts this signal to cause the master

port to wait.

Control Synchronizer Control Registers

Table 11-3: Control Synchronizer Register Map

The control data is read once at the start of each frame and is buffered inside the IP core, so the registers can be

safely updated during the processing of a frame.

Note: The width of each register of the frame reader is 32 bits.

Address

Register

Description

0

Control

• Bit 0 of this register is the

Go

bit. Setting this bit to 0 causes

the IP core to start passing through data.

• Bit 1 of this register is the interrupt enable. Setting this bit

to 1 enables the completion of writes interrupt.

1

Status

Bit 0 of this register is the

Status

bit, all other bits are unused.

2

Interrupt

Bit 1 of this register is the completion of writes interrupt bit,

all other bits are unused. Writing a 1 to bit 1 resets the

completion of writes interrupt.

11-6

Control Synchronizer Control Registers

UG-VIPSUITE

2015.05.04

Altera Corporation

Control Synchronizer IP Core