Altera Video and Image Processing Suite User Manual

Page 308

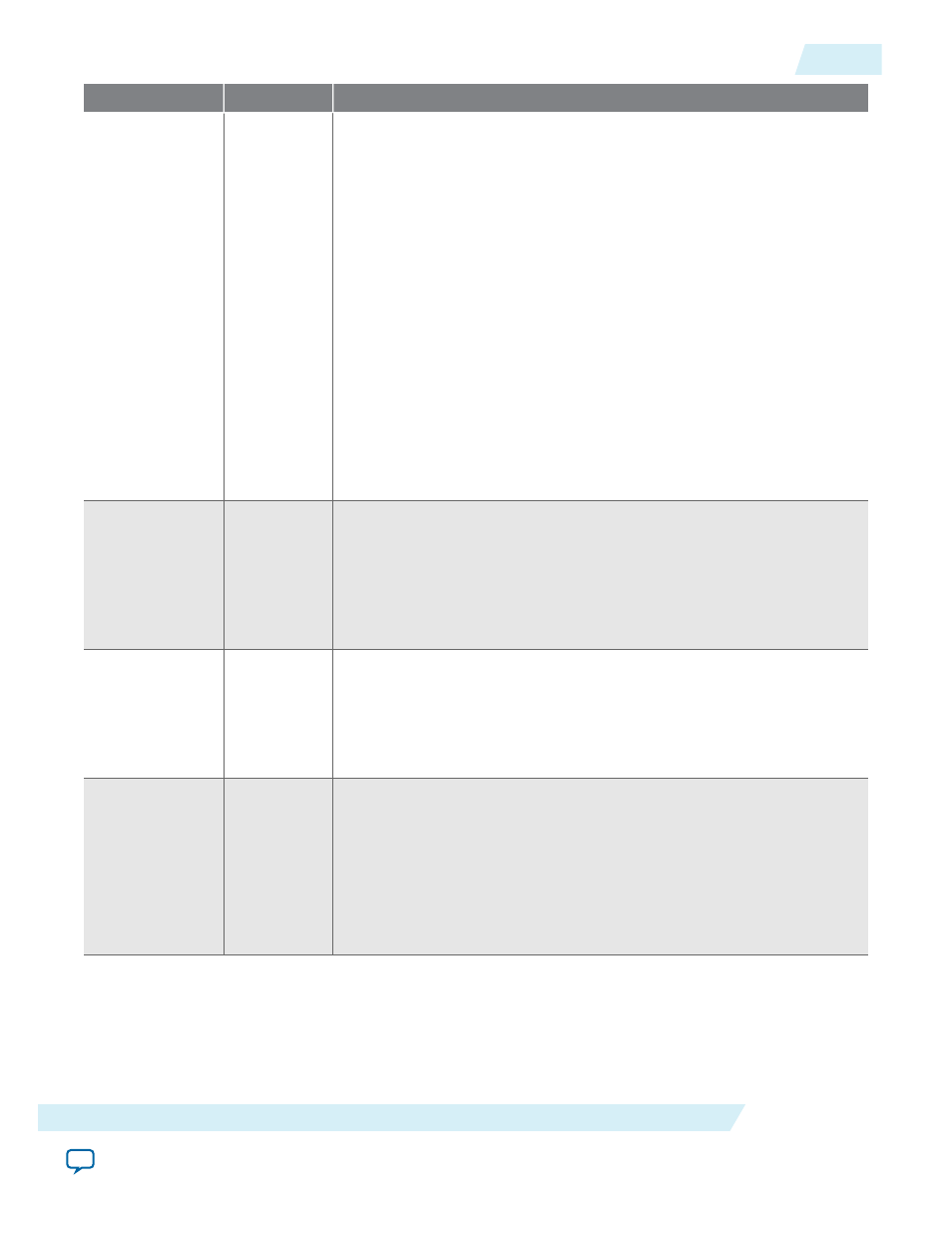

Date

Version

Changes

August 2014

14.0

• Added new IP cores: Clocked Video Output II, Clocked Video Input

II, Color Space Converter II, Mixer II, Frame Buffer II, Switch II, and

Test Pattern Generator II.

• Revised the performance and resource data for different configura‐

tions using Arria V and Cyclone V devices.

• Added information about IP catalog and removed information about

MegaWizard Plug-In Manager.

• Updated bit 5 of the

Status

register as unused for the Clocked Video

Input IP core.

• Corrected the formula for adjusting the filter function’s phase for the

Scaler II IP core.

• Consolidated the latency information for all IP cores in the Overview

chapter.

• Consolidated the stall behavior and error recovery information for all

IP cores in the Overview chapter.

• Moved the 'Video Formats' section from Clocked Video Input and

Output chapters to the Interfaces chapter.

February 2014

13.1

• Added information on 4:2:2 support.

• Added Design Guidelines section for the Broadcast Deinterlacer IP

core.

• Removed information about Arria GX, Cyclone, Cyclone II, Stratix,

Stratix GX, Stratix II, Stratix II GX, and all HardCopy devices. Altera

no longer supports these devices.

July 2013

13.0

• Added new IP cores: Broadcast Deinterlacer and Clipper II

• Removed Scaler IP core. This core is no longer supported in version

13.0 and later.

• Added information about the Add data enable signal parameter and

the

vid_de

signal for Clocked Video Input IP core.

April 2013

12.1.1

Added the following information for the Avalon-ST Video Monitor IP

core.

• Added description for packet visualization.

• Added explanation for Capture Rate per 1000000 option for monitor

settings.

• Added Capture video pixel data parameter.

• Added Control Bits entry to the register map.

UG-VIPSUITE

2015.05.04

Document Revision History

C-3

Additional Information

Altera Corporation