Video clipping signals, Video clipping signals -4 – Altera Video and Image Processing Suite User Manual

Page 130

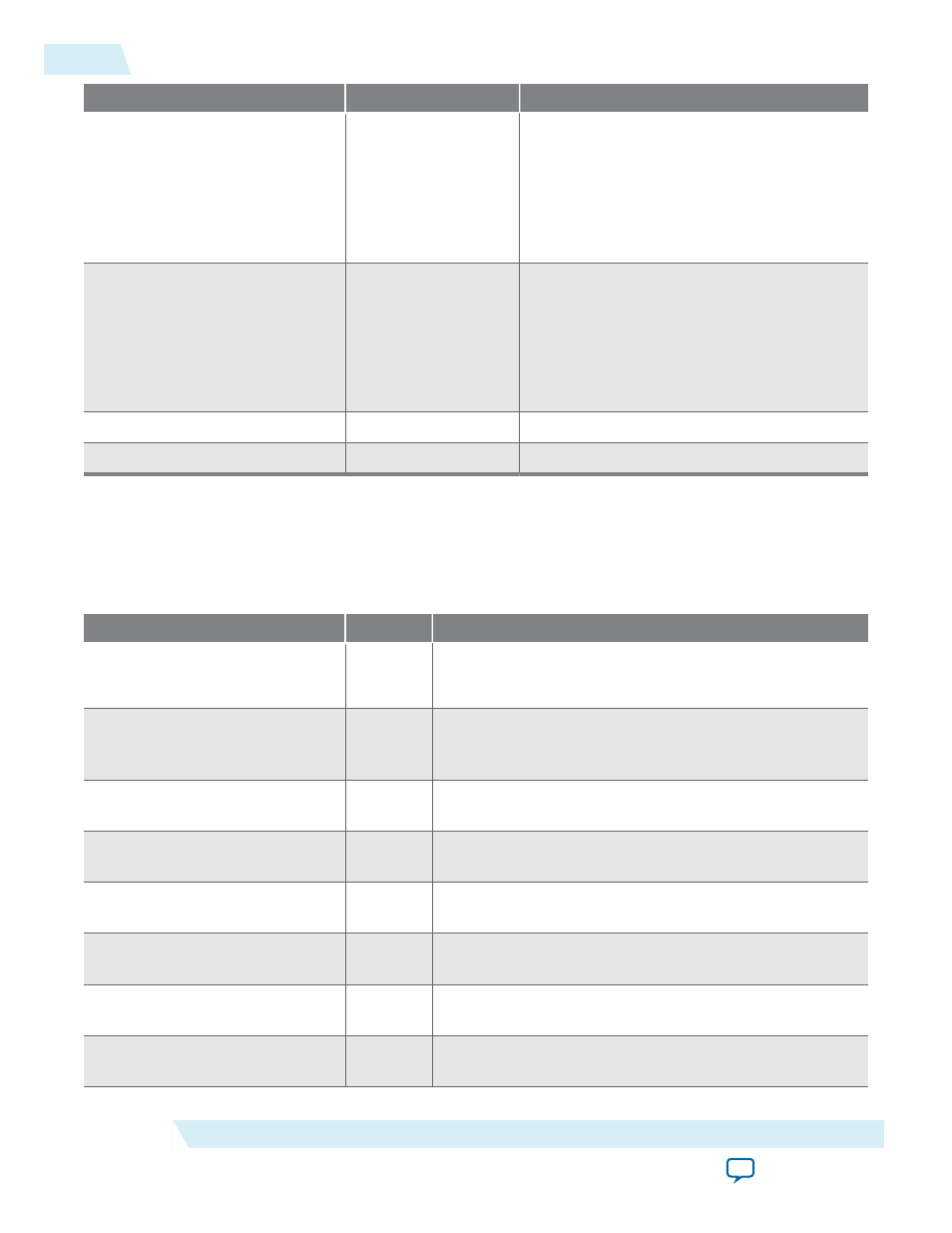

Parameter

Value

Description

Right offset

0–1080, Default = 10

Specify the x coordinate for the right edge of

the clipping rectangle. 0 is the right edge of

the input area.

Note: The left and right offset values

must be less than or equal to the

input image width.

Bottom offset

0–1080, Default = 10

Specify the y coordinate for the bottom edge

of the clipping rectangle. 0 is the bottom edge

of the input area.

Note: The top and bottom offset values

must be less than or equal to the

input image height.

Width

0–1920, Default = 10

Specify the width of the clipping rectangle.

Height

0–1080, Default = 10

Specify the height of the clipping rectangle.

Video Clipping Signals

Table 8-3: Common Signals

These signals apply to both Clipper and Clipper II IP cores.

Signal

Direction

Description

•

clock

(Clipper)

•

main_clock

(Clipper II)

Input

The main system clock. The IP core operates on the rising

edge of this signal.

•

reset

(Clipper)

•

main_reset

(Clipper II)

Input

The IP core asynchronously resets when this signal is high.

You must deassert this signal synchronously to the rising

edge of the clock signal.

din_data

Input

din

port Avalon-ST

data

bus. This bus enables the

transfer of pixel data into the IP core.

din_endofpacket

Input

din

port Avalon-ST

endofpacket

signal. This signal

marks the end of an Avalon-ST packet.

din_ready

Output

din

port Avalon-ST

ready

signal. This signal indicates

when the IP core is ready to receive data.

din_startofpacket

Input

din

port Avalon-ST

startofpacket

signal. This signal

marks the start of an Avalon-ST packet.

din_valid

Input

din

port Avalon-ST

valid

signal. This signal identifies the

cycles when the port must enter data.

dout_data

Output

dout

port Avalon-ST

data

bus. This bus enables the

transfer of pixel data out of the IP core.

8-4

Video Clipping Signals

UG-VIPSUITE

2015.05.04

Altera Corporation

Video Clipping IP Cores