Avalon-st video monitor control registers, Avalon-st video monitor control registers -6 – Altera Video and Image Processing Suite User Manual

Page 267

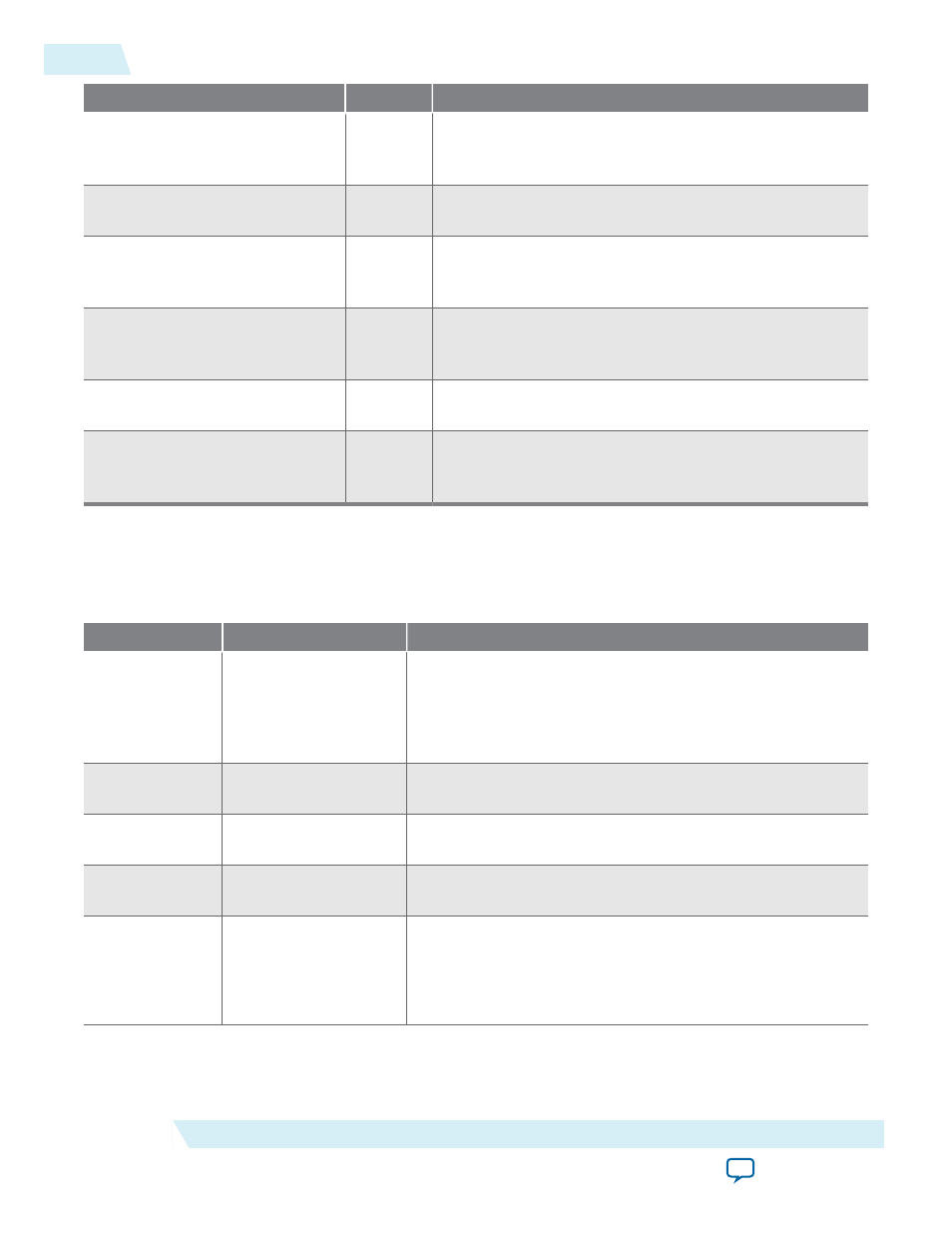

Signal

Direction

Description

control_read

Input

control

slave port Avalon-MM

read

signal. The IP core

asserts this signal to indicate read requests from the

master to the system interconnect fabric.

controlreaddata

Output

control

slave port Avalon-MM

readdata

bus. These

input lines carry data for read transfers.

control_readdatavalid

Output

control

slave port Avalon-MM

readdatavalid

signal.

The system interconnect fabric asserts this signal when the

requested read data has arrived.

control_write

Input

control

slave port Avalon-MM

write

signal. The IP core

asserts this signal to indicate write requests from the

master to the system interconnect fabric.

control_writedata

Input

control

slave port Avalon-MM

write

signal. The IP core

uses these input lines for write transfers.

control_waitrequest

Output

control

slave port Avalon-MM

waitrequest

signal. The

system interconnect fabric asserts this signal to cause the

master port to wait.

Avalon-ST Video Monitor Control Registers

Table 21-4: Avalon-ST Video Monitor Register Map

Address

Register

Description

0

Identity

Read only register—manufacturer and monitor identities.

• Bits 11:0 are identities for the manufacturer, Altera = 0×6E

• Bits 27:12 are identities for the monitor, Avalon-ST video

monitor = 0×110

1

Configuration

Information

For use of System Console only.

2

Configuration

Information

For use of System Console only.

3

Configuration

Information

For use of System Console only.

4

Control

• Setting bits 0 and 8 to 1 sends statistic counters.

• Setting bits 0 and 9 to 1 sends up to first 6 beats on the

Avalon-ST data bus.

• Setting bit 0 to 0 disables both the statistics and beats.

21-6

Avalon-ST Video Monitor Control Registers

UG-VIPSUITE

2015.05.04

Altera Corporation

Avalon-ST Video Monitor IP Core