Altera Video and Image Processing Suite User Manual

Page 188

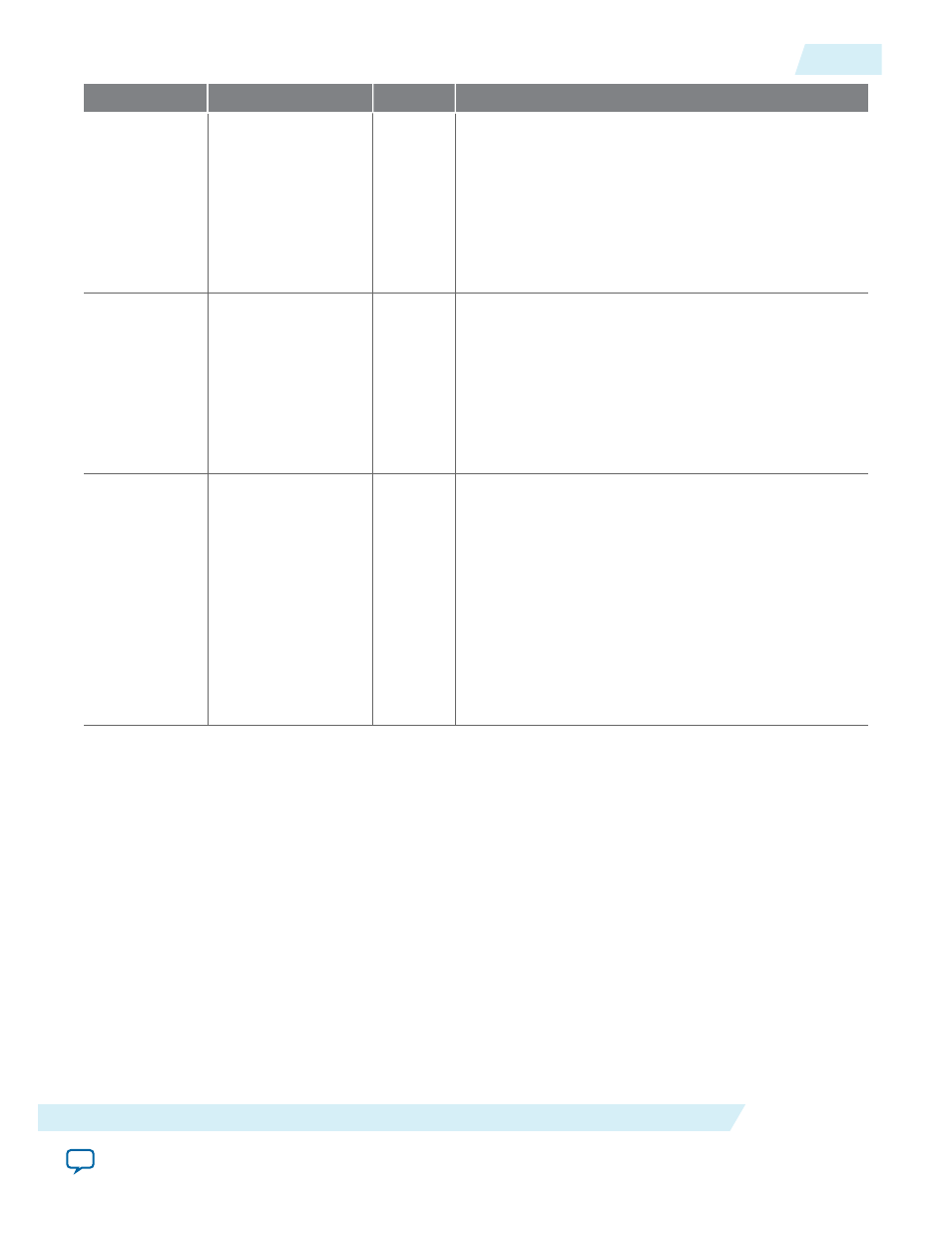

Address

Register

RO/RW

Description

22

History Minimum

Value

RW

The cadence bias for a given pixel. Setting a lower value

biases the pixels toward film, and setting a higher value

biases the pixels toward video. The pixel SAD values

are scaled according to the recent history that gives the

frames an affinity for their historical state.

Range: 0–3

Power on value: 3

23

History Maximum

Value

RW

The cadence bias for a given pixel. Setting a lower value

bias the pixels toward film and setting a higher bias the

pixels toward video. The value for this register must be

higher than the value for the

History Minimum Value

register.

Range: 3–7

Power on value: 7

24

SAD Mask

RW

When detecting cadences, the SAD values are AND’ed

with this value. This value allows the LSBs to be

masked off to provide protection from noise.

For example, use binary 11_1111_0000 to ignore the

lower 4 bits of the SAD data when detecting cadences.

This register works orthogonally from the

Motion

Shift

register (Offset 25), which affects both motion

calculation in general AND cadence detection.

Range: 512–1023

Power on value: 960

UG-VIPSUITE

2015.05.04

Deinterlacing Control Registers

12-29

Deinterlacing IP Cores

Altera Corporation