Altera Video and Image Processing Suite User Manual

Page 309

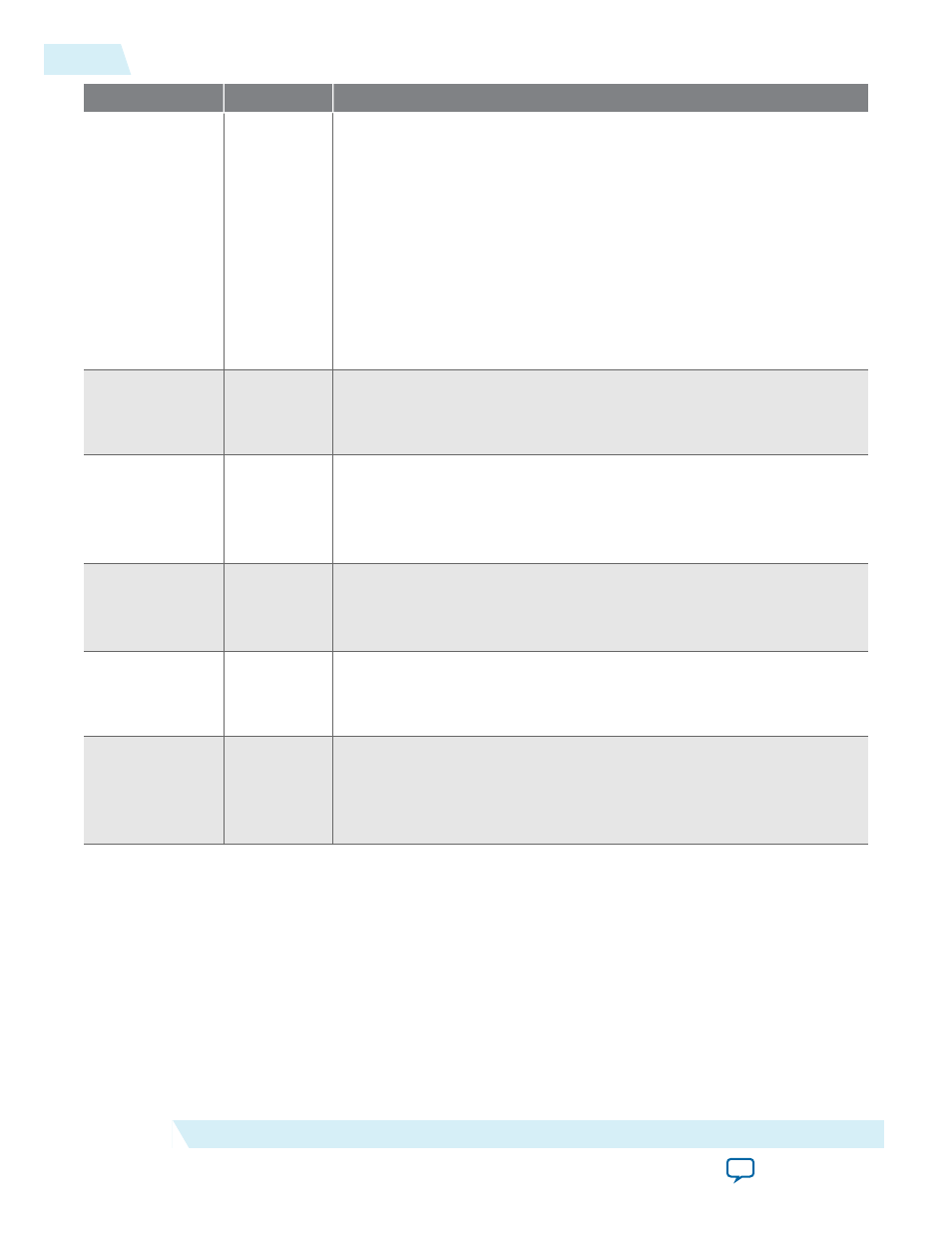

Date

Version

Changes

January 2013

12.1

• Added Deinterlacer II Sobel-Based HQ Mode information for the

Deinterlacer II IP core.

• Updated Table 1–17 to include latest Deinterlacer II IP core perform‐

ance figures for Cyclone IV and Stratix V devices.

• Edited the description of the

rst

signal for the Clocked Video Output

IP core.

• Added a note to explain that addresses 4, 5, and 6 in the Frame Buffer

control register map are optional and visible only when the GUI

option is checked.

• Updated Table 23–4 to include the functionality of address 0 in the

register map.

July 2012

12.0

• Added new IP cores: Avalon-ST Video Monitor and Trace System.

• Added information on the edge-adaptive scaling algorithm feature for

the Scaler II IP core.

February 2012

11.1

• Reorganized the user guide.

• Added new appendixes: “Avalon-ST Video Verification IP Suite” and

“Choosing the Correct Deinterlacer”.

• Updated Table 1-1 and Table 1-3.

May 2011

11.0

• Added new IP core: Deinterlacer II.

• Added new polyphase calculation method for Scaler II IP core.

• Final support for Arria II GX, Arria II GZ, and Stratix V devices.

January 2011

10.1

• Added new IP core: Scaler II.

• Updated the performance figures for Cyclone IV GX and Stratix V

devices.

July 2010

10.0

• Preliminary support for Stratix V devices.

• Added new IP core: Interlacer.

• Updated Clocked Video Output and Clocked Video Input IP cores to

insert and extract ancillary packets.

C-4

Document Revision History

UG-VIPSUITE

2015.05.04

Altera Corporation

Additional Information