Altera Video and Image Processing Suite User Manual

Page 51

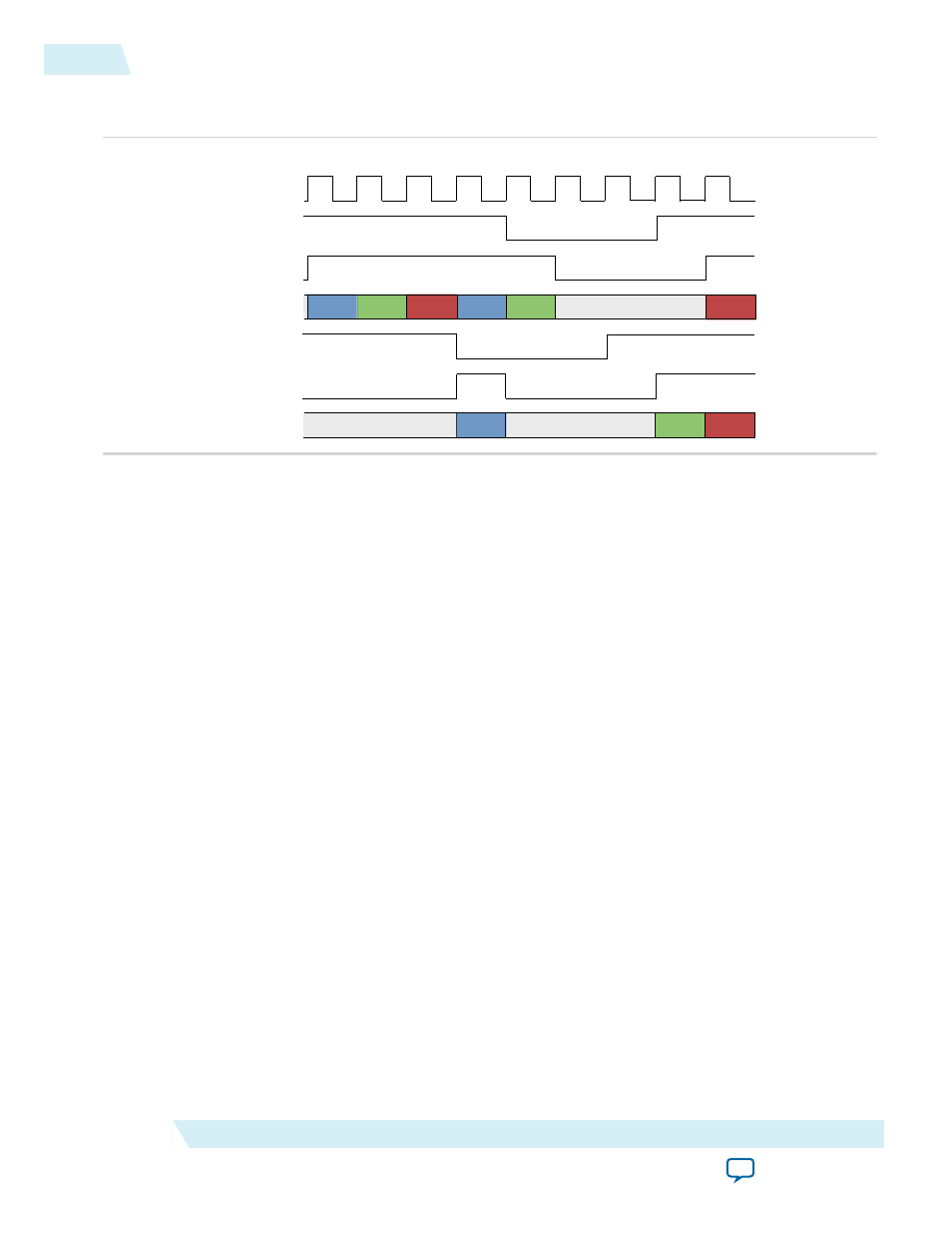

Figure 2-17: Timing Diagram Showing R’G’B’ Transferred in Sequence

The figure shows how a number of pixels from the middle of a frame are processed.

clock

din_ready

din_valid

din_data 7:0

R

m,n

R

G

0,0

G

m,n

B

m,n

B

m+1,n

1.

2.

3.

4.

5.

6.

7.

dout_ready

dout_valid

dout_data 7:0

R

8.

9.

G

1,0

G

m+1,n

G

0,0

G

m,n

B

m,n

m+1,n

m,n

This example is similar to example one except that it is configured to accept data in sequence rather than

parallel. The signals shown in the timing diagram are therefore the same but with the exception that the

two data ports are only 8 bits wide.

The sequence of events for this example:

1. Initially,

din_ready

is logic '1'. The source driving the input port sets

din_valid

to logic '1' and puts

the blue color value B

m,n

on the

din_data

port.

2. The source holds

din_valid

at logic '1' and the green color value G

m,n

is input.

3. The corresponding red color value R

m,n

is input.

4. The IP core sets

dout_valid

to logic '1' and outputs the blue color value of the first processed color

sample on the

dout_data

port. Simultaneously the sink connected to the output port sets

dout_ready

to logic '0'. The Avalon Interface Specifications state that sinks may set ready to logic '0' at any time, for

example because the sink is a FIFO and it has become full.

5. The IP core sets

dout_valid

to logic '0' and stops putting data on the

dout_data

port because the sink

is not ready for data. The IP core also sets

din_ready

to logic '0' because there is no way to output data

and the IP core must stop the source from sending more data before it uses all internal buffer space.

The sink holds

din_valid

at logic '1' and transmits one more color sample G

m+1,n

, which is legal

because the ready latency of the interface means that the change in the IP core's readiness does not take

effect for one clock cycle.

6. Both the input and output interfaces do not transfer any data: the IP core stalls to wait for the sink.

7. The sink sets

dout_ready

to logic '1'. This could be because space has been cleared in a FIFO.

8. The IP core sets

dout_valid

to logic '1' and resumes transmitting data. Now that the flow of data is

unimpeded again, it sets

din_ready

to logic '1'.

9. The source responds to

din_ready

by setting

din_valid

to logic '1' and resuming data transfer.

2-24

Packet Transfer Examples

UG-VIPSUITE

2015.05.04

Altera Corporation

Interfaces