Altera Video and Image Processing Suite User Manual

Page 193

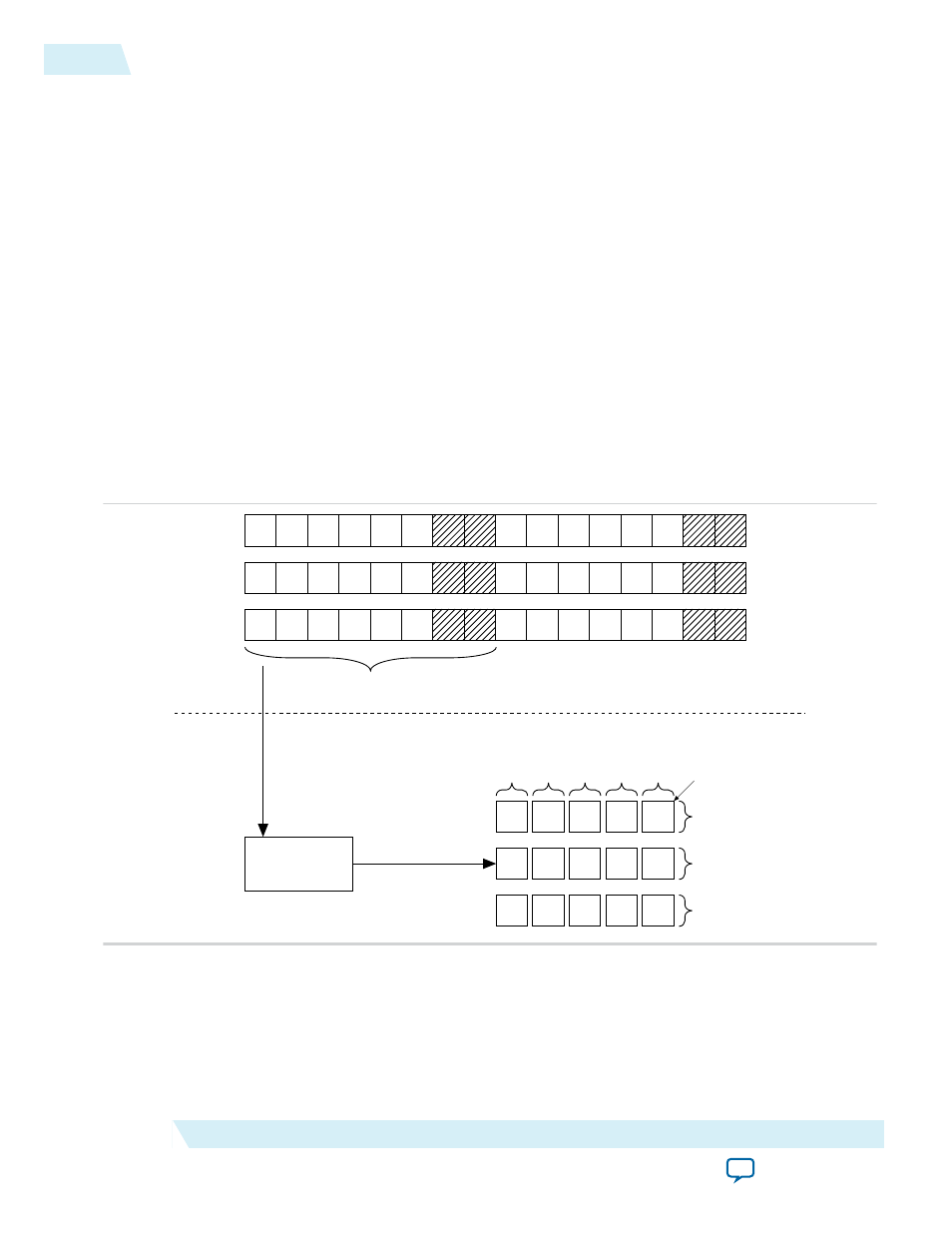

width during compilation. Each word can only contain whole single-cycle color patterns. The words

cannot contain partial single-cycle color patterns. Any bits of the word that cannot fit another whole

single-cycle color pattern are not used.

Also, you must configure the Frame Reader IP core with the starting address of the video frame in

memory, and the width, height, and interlaced values of the control data packet to be produced as outputs

before each video data packet.

The raw data that comprises a video frame in external memory is stored as a set of single-cycle color

patterns. In memory, the single-cycle color patterns must be organized into word-sized sections. Each of

these word-sized sections must contain as many whole samples as possible, with no partial single-cycle

color patterns. Unused bits are in the most significant portion of the word-sized sections. Single-cycle

color patterns in the least significant bits are output first. The frame is read with words at the starting

address first.

Frame Reader Output Pattern and Memory Organization

Figure 13-1: Frame Reader Output Pattern and Memory Organization

The figure shows the output pattern and memory organization for a Frame Reader IP core, which is

configured for 8 bits per pixel per color plane, 3 color planes on parallel, and master port width of 64.

28

29

27

24

25

26

16

17

15

12

13

14

4

5

3

0

1

2

34

35

33

30

31

32

22

23

21

18

19

20

10

11

9

6

7

8

11

10

7

8

9

6

5

12

13

14

4

3

0

Start

Address

64-Bit Word

Frame Reader

MegaCore

Avalon Memory Map

Read Master Port

Avalon

Streaming Output

Single Cycle Color

External Memory

8 Bits

8 Bits

8 Bits

Cycle 4

Cycle 3

Cycle 2

Cycle 1

Cycle 0

1

2

The Avalon Slave control port allows the specification of up to two memory locations, each containing a

video frame. Switching between these memory locations is performed with a single register. This allows

the Frame Reader IP core to read a series of frames from different memory addresses without having to

set multiple registers within the period of a single frame. This feature is useful when reading very small

frames, and helps to simplify control timing. To aid the timing of control instructions and to monitor the

13-2

Frame Reader Output Pattern and Memory Organization

UG-VIPSUITE

2015.05.04

Altera Corporation

Frame Reader IP Core