Video switching control registers, Video switching control registers -5 – Altera Video and Image Processing Suite User Manual

Page 241

Signal

Direction

Description

alpha_out_N_ready

Input

alpha_out

port Avalon-ST

ready

signal. The downstream

device asserts this signal when it is able to receive data.

alpha_out_N_startofpacket

Output

alpha_out

port Avalon-ST

startofpacket

signal. This

signal marks the start of an Avalon-ST packet.

alpha_out_N_valid

Output

alpha_out

port Avalon-ST

valid

signal. The IP core

asserts this signal when it produces data.

Video Switching Control Registers

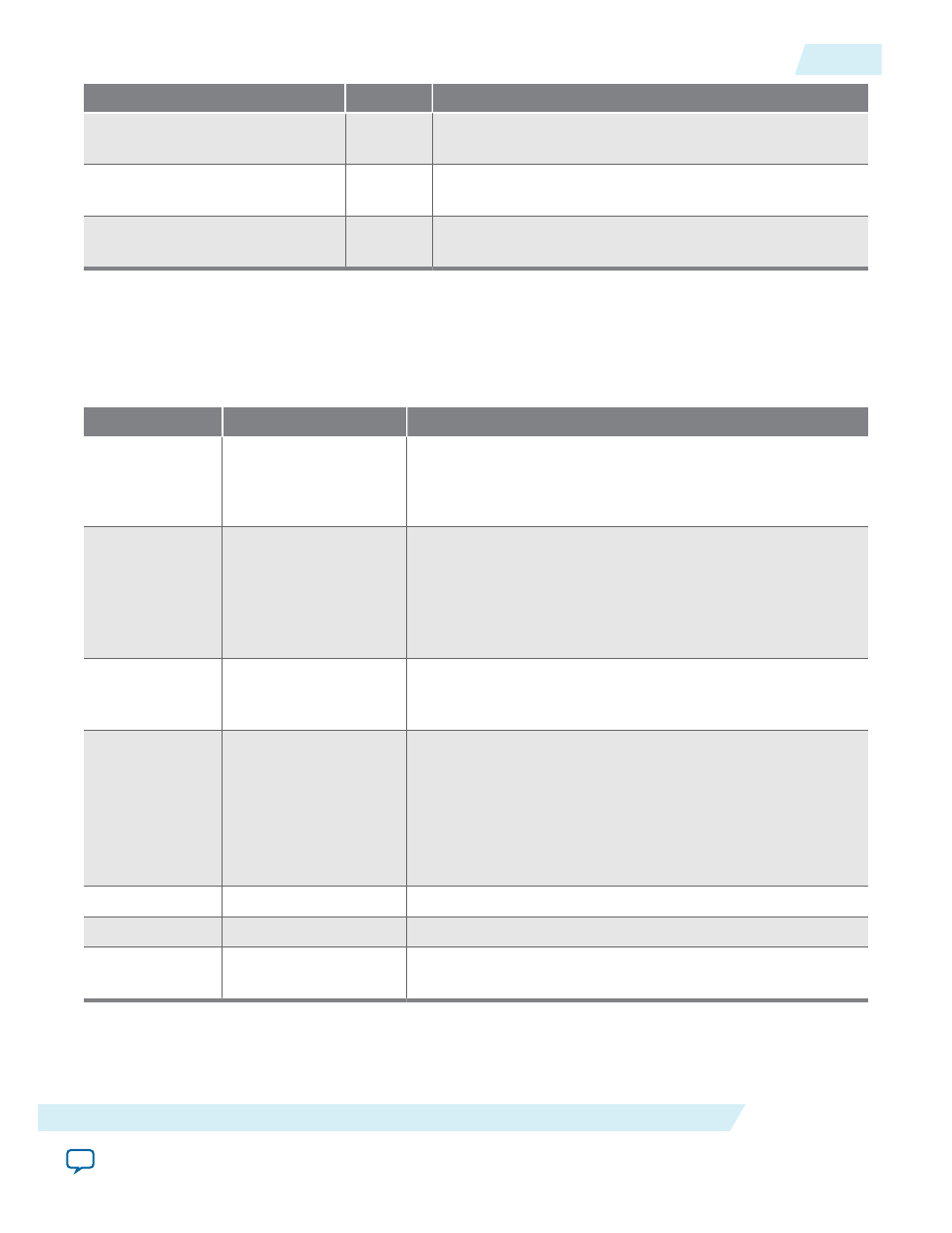

Table 18-5: Switch Control Register Map

The table below describes the control register map for Switch IP core.

Address

Register

Description

0

Control

Bit 0 of this register is the

Go

bit, all other bits are unused.

• Writing a 1 to bit 0 starts the IP core.

• Writing a 0 to bit 0 stops the IP core.

1

Status

Bit 0 of this register is the

Status

bit, all other bits are unused.

• Reading a 1 from bit 0 indicates the IP core is running—

video is flowing through it.

• Reading a 0 from bit 0 indicates that the IP has stopped

running.

2

Output Switch

Writing a 1 to bit 0 indicates that the video output streams

must be synchronized; and the new values in the output

control registers must be loaded.

3

Dout0 Output Control

A one-hot value that selects which video input stream must

propagate to this output. For example, for a 3-input switch:

• 3'b000 = no output

• 3'b001 = din_0

• 3'b010 = din_1

• 3'b100 = din_2

4

Dout1 Output Control

As

Dout0 Output Control

but for output

dout1

.

...

...

...

15

Dout12 Output

Control

As

Dout0 Output Control

but for output

dout12

.

UG-VIPSUITE

2015.05.04

Video Switching Control Registers

18-5

Video Switching IP Cores

Altera Corporation