Altera Video and Image Processing Suite User Manual

Page 24

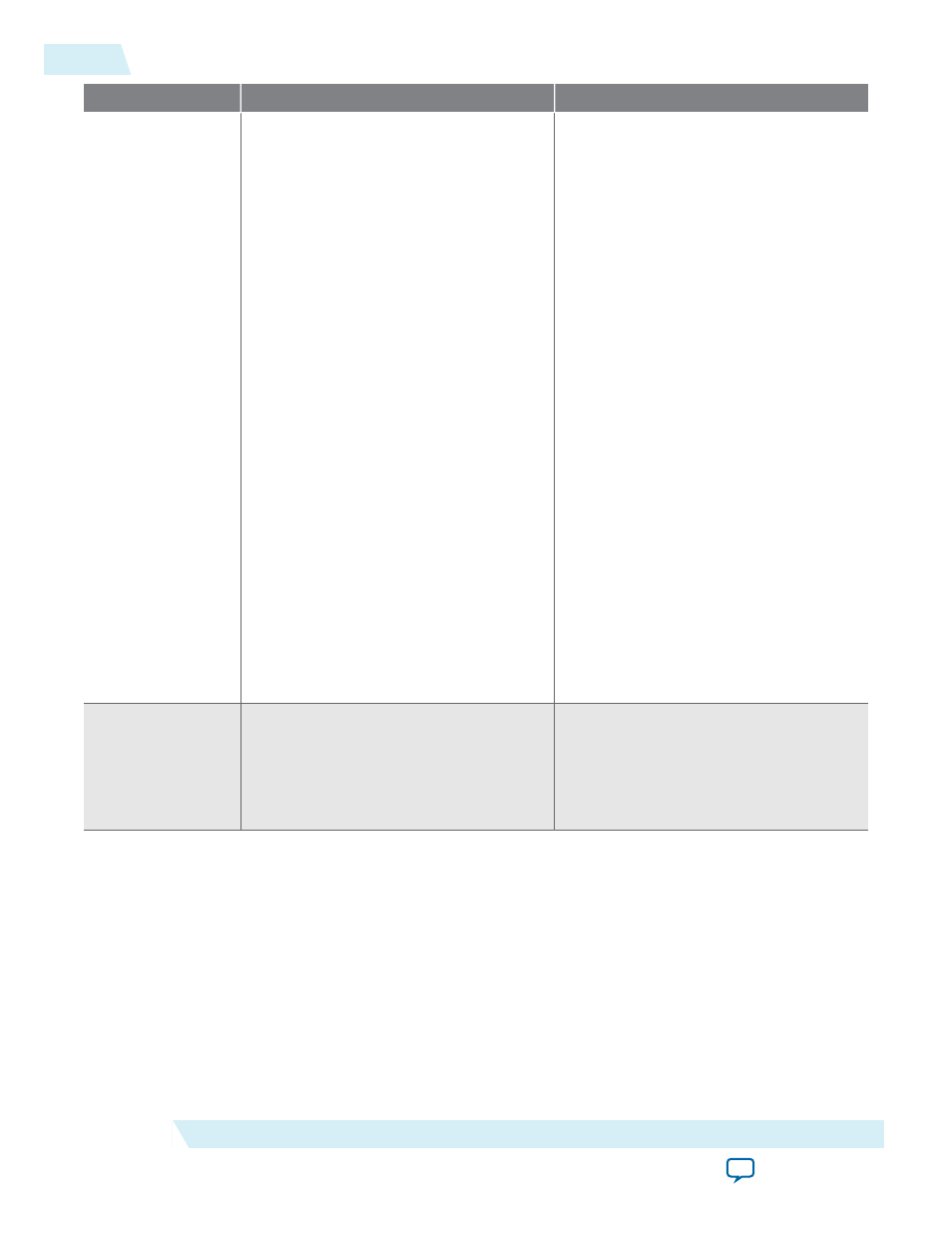

IP Core

Stall Behavior

Error Recovery

Deinterlacer II/

Broadcast

Deinterlacer

Stores input video fields in the external

memory and concurrently uses these input

video fields to construct deinterlaced

frames.

• Stalls up to 50 clock cycles for the first

output frame.

• Additional delay of one line for second

output frame because the IP core

generates the last line of the output

frame before accepting the first line of

the next input field.

• Delay of two lines for the following

output frames, which includes the one

line delay from the second output frame.

• For all subsequent fields, the delay

alternates between one and two lines.

• Receiving an

endofpacket

signal too

early :

• The IP core generates a line with

the correct length.

• The video data in the output

frame is valid up to the point

where the IP core receives the

endofpacket

signal.

• The IP core then stops generating

output until it receives the next

startofpacket

signal.

• Receiving a late

endofpacket

signal:

• The IP core completes generating

the current output frame with the

correct number of lines as

indicated by the last control

packet.

• The IP core discards the

subsequent input lines.

• Once it receives a

startofpacket

signal, the IP core performs a soft

reset and it loses the stored

cadence or motion values.

• The IP core resumes deinterlacing

when it receives the next

startofpacket

signal.

Frame Reader

• Stalls the output for several tens of cycles

before producing each video data packet.

• Stalls the output where there is

contention for access to external

memory.

The IP core can be stalled due to

backpressure, without consequences and

it does not require error recovery.

1-18

Stall Behavior and Error Recovery

UG-VIPSUITE

2015.05.04

Altera Corporation

Video and Image Processing Suite Overview