Altera Video and Image Processing Suite User Manual

Page 86

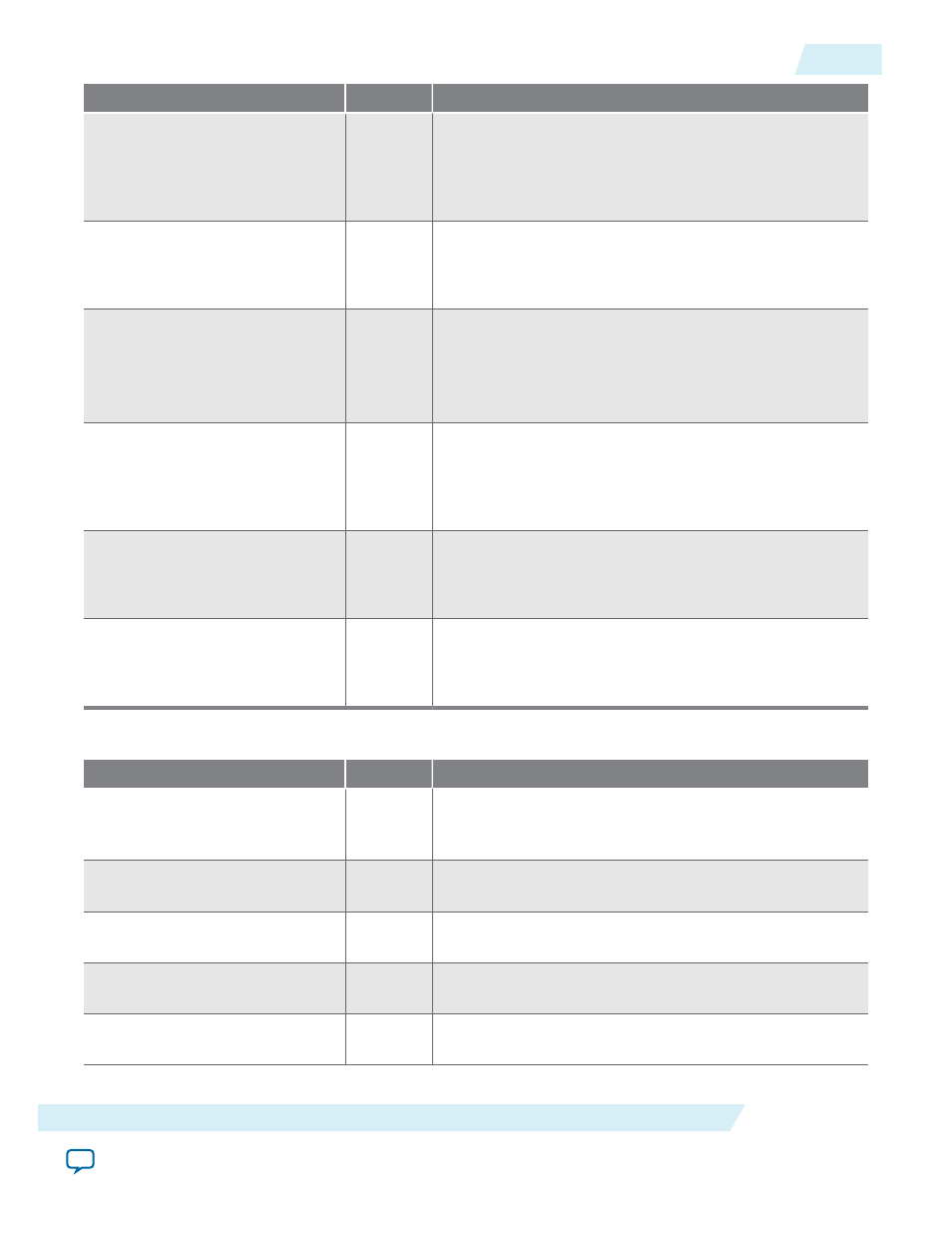

Signal

Direction

Description

av_read

Input

control

slave port Avalon-MM read signal. When you

assert this signal, the

control

port drives new data onto

the read data bus.

Note: Present only if you turn on Use control port.

av_readdata

Output

control

slave port Avalon-MM read data bus. These

output lines are used for read transfers.

Note: Present only if you turn on Use control port.

av_waitrequest

Output

control

slave port Avalon-MM wait request bus. This

signal indicates that the slave is stalling the master transac‐

tion.

Note: Present only if you turn on Use control port.

av_write

Input

control

slave port Avalon-MM

write

signal. When you

assert this signal, the

control

port accepts new data from

the write data bus.

Note: Present only if you turn on Use control port.

av_writedata

Input

control

slave port Avalon-MM write data bus. These

input lines are used for write transfers.

Note: Present only if you turn on Use control port.

av_byteenable

Input

control

slave port Avalon-MM

byteenable

bus. These

lines indicate which bytes are selected for write and read

transactions.

Table 4-16: Clocked Video Input Signals

Signal

Direction

Description

rst

Input

The IP core asynchronously resets when you assert this

signal. You must deassert this signal synchronously to the

rising edge of the clock signal.

is_clk

Input

Clock signal for Avalon-ST ports

dout

and

control

. The

IP core operates on the rising edge of the

is_clk

signal.

is_data

Output

dout

port Avalon-ST

data

bus. This bus enables the

transfer of pixel data out of the IP core.

is_eop

Output

dout

port Avalon-ST

endofpacket

signal. This signal is

asserted when the IP core is ending a frame.

is_ready

Input

dout

port Avalon-ST

ready

signal. The downstream

device asserts this signal when it is able to receive data.

UG-VIPSUITE

2015.05.04

Clocked Video Interface Signals

4-27

Clocked Video Interface IP Cores

Altera Corporation