Altera Video and Image Processing Suite User Manual

Page 184

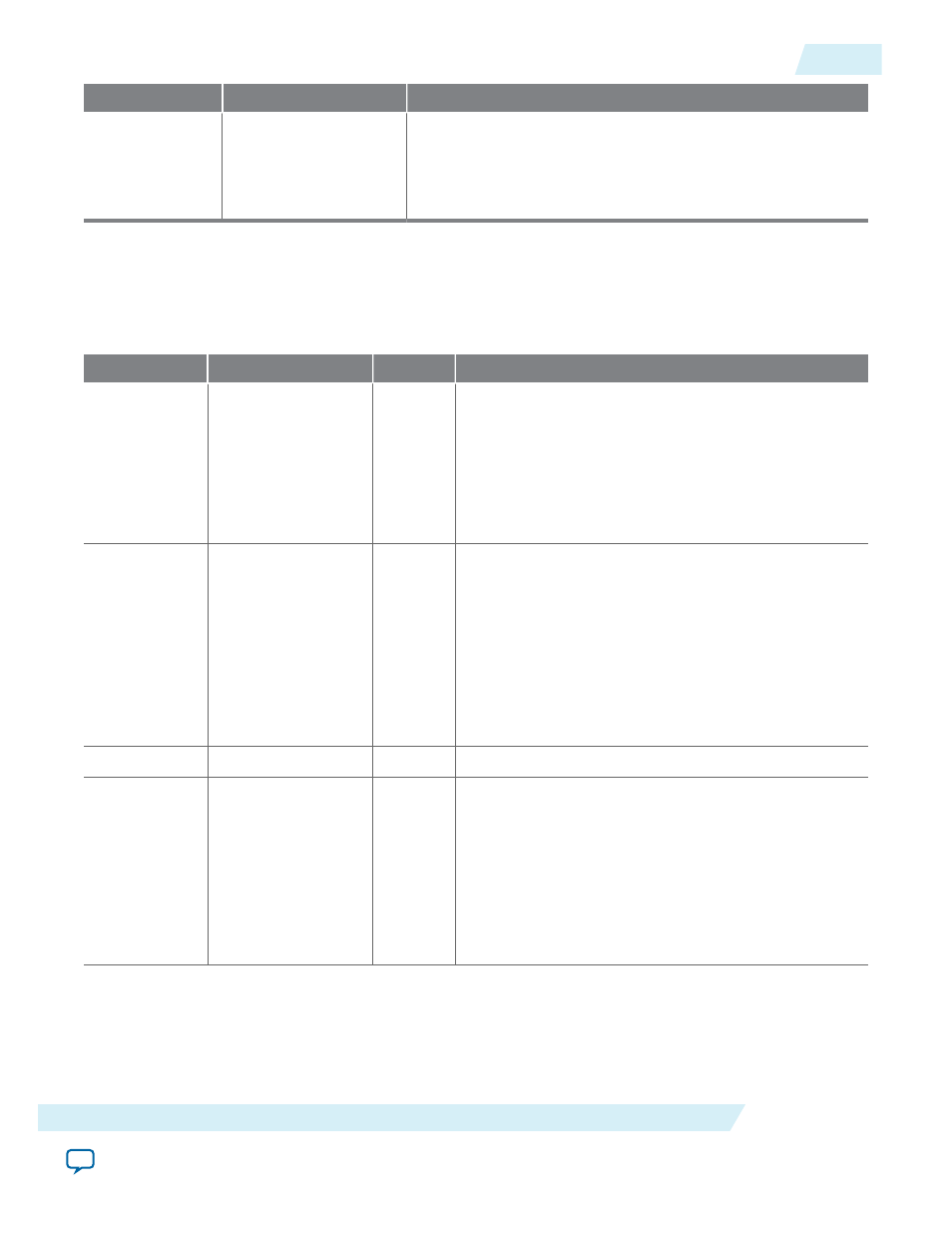

Address

Register

Description

4

Cadence detected

• Reading a 1 from bit 0, indicates that the Deinterlacer II IP

core has detected a cadence and is performing reverse

telecine.

• Reading a 0 indicates otherwise.

Table 12-11: Broadcast Deinterlacer Control Register Map

The table below describes the Broadcast Deinterlacer IP core control register map for runtime control of the

motion-adaptive algorithm. The Broadcast Deinterlacer reads the control data once at the start of each frame and

buffers the data inside the IP core. The registers may safely update during the processing of a frame. Use these

registers in software to obtain the best deinterlacing quality.

Address

Register

RO/RW

Description

0

Control

RW

Bit 0 of this register is the

Go

bit, all other bits are

unused.

Setting this bit to 0 causes the Broadcast Deinterlacer

IP core to stop the next time that control information

is read.

Power on value: 0

1

Status

RO

Bit 0 of this register is the

Status

bit, all other bits are

unused.

• The Broadcast Deinterlacer IP core sets this address

to 0 between frames when the

Go

bit is set to 0.

• The Broadcast Deinterlacer IP core sets this address

to 1 while the core is processing data and cannot be

stopped.

Power on value: 0

2

Reserved

RO

This register is reserved for future use.

3

Cadence Detected

RO

• When polled, the least significant bit (LSB) to 1,

indicates the Broadcast Deinterlacer IP core has

detected a 3:3 or 2:2 cadence and is performing

reverse telecine.

• Bit 0 indicates otherwise.

Range: 0–1

Power on value: 0

UG-VIPSUITE

2015.05.04

Deinterlacing Control Registers

12-25

Deinterlacing IP Cores

Altera Corporation