Altera Video and Image Processing Suite User Manual

Page 82

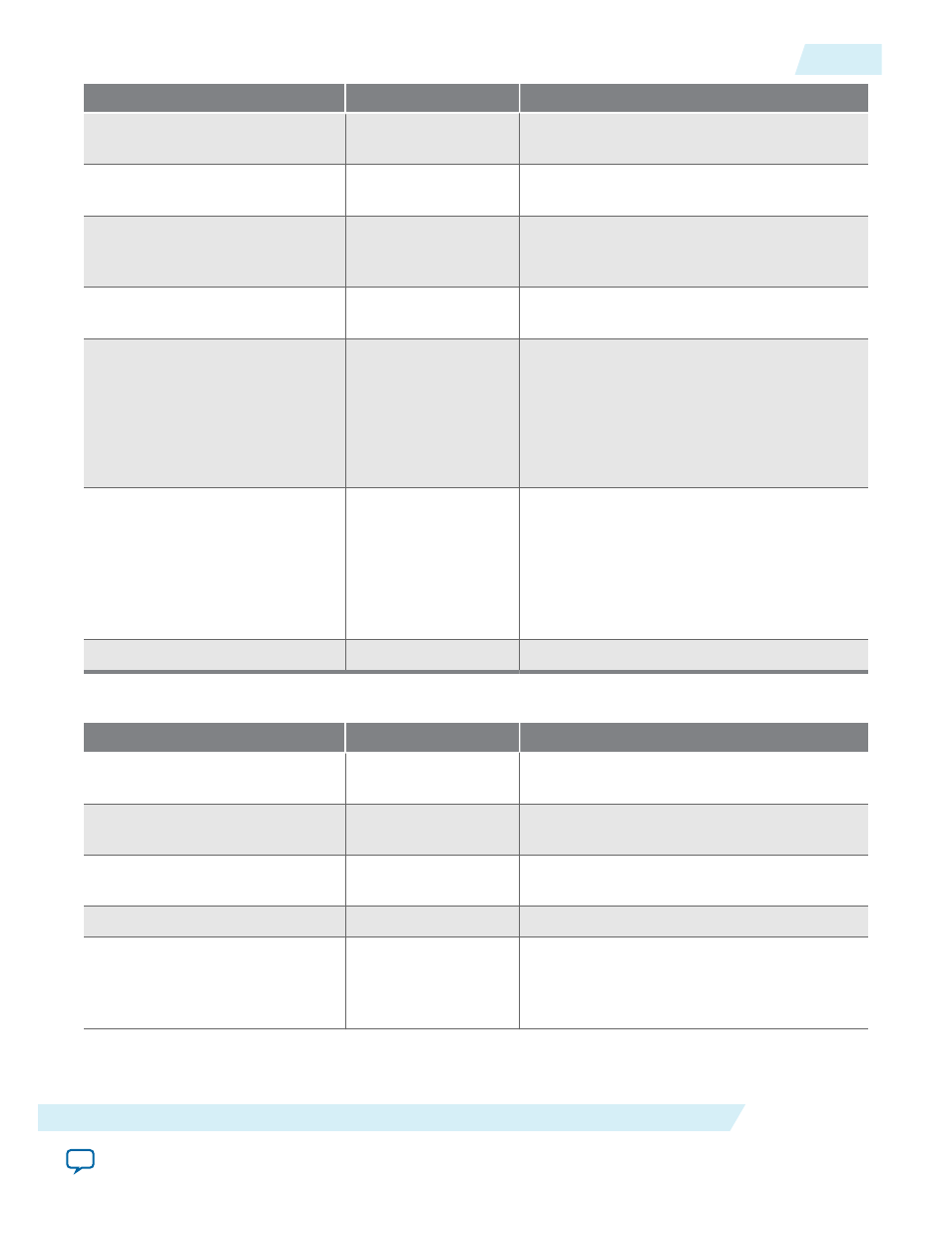

Parameter

Value

Description

Pixel FIFO size

32–(memory limit),

Default = 1920

Specify the required FIFO depth in pixels,

(limited by the available on-chip memory).

FIFO level at which to start

output

0–(memory limit),

Default = 0

Specify the fill level that the FIFO must have

reached before the output video starts.

Video in and out use the same

clock

On or Off

Turn on if you want to use the same signal for

the input and output video image stream

clocks.

Use control port

On or Off

Turn on to use the optional Avalon-MM

control port.

Run-time configurable video

modes

1–14, Default = 1

Specify the number of run-time configurable

video output modes that are required when

you are using the Avalon-MM control port.

Note: This parameter is available only

when you turn on Use control

port.

Accept synchronization outputs • No

• Yes

Specifies whether the synchronization

outputs (

sof

,

sof_locked

) from the CVI IP

cores are used:

• No—Synchronization outputs are not

used

• Yes—Synchronization outputs are used

Width of vid_std

1–16, Default = 1

Select the width of the

vid_std

bus, in bits.

Table 4-13: Clocked Video Output II Parameter Settings

Parameter

Value

Description

Image width/Active pixels

32–8192, Default =

1920

Specify the image width by choosing the

number of active pixels.

Image height/Active lines

32–8192, Default =

1200

Specify the image height by choosing the

number of active lines.

Bits per pixel per color plane

4–20, Default = 8

Select the number of bits per pixel (per color

plane).

Number of color planes

1–4, Default = 3

Select the number of color planes.

Color plane transmission format • Sequence

• Parallel

Specify whether to transmit the color planes

in sequence or in parallel. If you select

multiple pixels in parallel, then select

Parallel.

UG-VIPSUITE

2015.05.04

Clocked Video Interface Parameter Settings

4-23

Clocked Video Interface IP Cores

Altera Corporation