Interlacer control registers, Interlacer control registers -4 – Altera Video and Image Processing Suite User Manual

Page 221

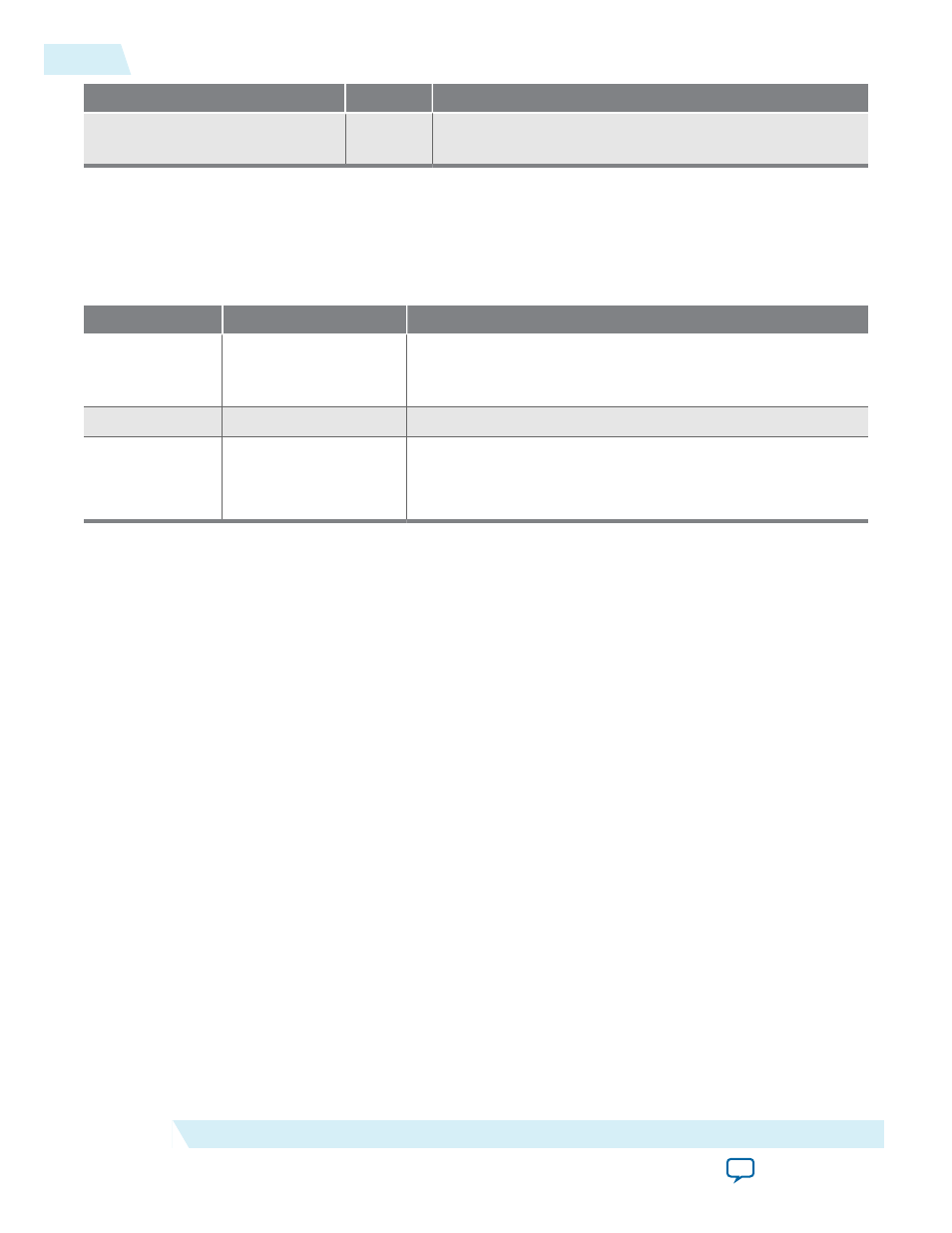

Signal

Direction

Description

control_av_writedata

Input

control

slave port Avalon-MM

writedata

bus. The IP

core uses these input lines for write transfers.

Interlacer Control Registers

Table 16-4: Interlacer Register Map

The control interface is 8 bits wide but the Interlacer IP core only uses bit 0 of each addressable register.

Address

Register

Description

0

Control

Bit 0 of this register is the

Go

bit. All other bits are unused.

Setting this bit to 1 causes the IP core to pass data through

without modification.

1

Status

Bit 0 of this register is the

Status

bit, all other bits are unused.

2

Progressive pass-

through

Setting bit 0 to 1 disables the Interlacer IP core. When

disabled, progressive inputs are propagated without modifica‐

tion.

16-4

Interlacer Control Registers

UG-VIPSUITE

2015.05.04

Altera Corporation

Interlacer IP Core

- MAX 10 JTAG (15 pages)

- MAX 10 Power (21 pages)

- Unique Chip ID (12 pages)

- Remote Update IP Core (43 pages)

- Device-Specific Power Delivery Network (28 pages)

- Device-Specific Power Delivery Network (32 pages)

- Hybrid Memory Cube Controller (69 pages)

- ALTDQ_DQS IP (117 pages)

- MAX 10 Embedded Memory (71 pages)

- MAX 10 Embedded Multipliers (37 pages)

- MAX 10 Clocking and PLL (86 pages)

- MAX 10 FPGA (26 pages)

- MAX 10 FPGA (56 pages)

- USB-Blaster II (22 pages)

- GPIO (22 pages)

- LVDS SERDES (27 pages)

- User Flash Memory (33 pages)

- ALTDQ_DQS2 (100 pages)

- Avalon Tri-State Conduit Components (18 pages)

- Cyclone V Avalon-MM (166 pages)

- Cyclone III FPGA Starter Kit (36 pages)

- Cyclone V Avalon-ST (248 pages)

- Stratix V Avalon-ST (286 pages)

- Stratix V Avalon-ST (293 pages)

- DDR3 SDRAM High-Performance Controller and ALTMEMPHY IP (10 pages)

- Arria 10 Avalon-ST (275 pages)

- Avalon Verification IP Suite (224 pages)

- Avalon Verification IP Suite (178 pages)

- FFT MegaCore Function (50 pages)

- DDR2 SDRAM High-Performance Controllers and ALTMEMPHY IP (140 pages)

- Floating-Point (157 pages)

- Integer Arithmetic IP (157 pages)

- Embedded Peripherals IP (336 pages)

- JESD204B IP (158 pages)

- Low Latency Ethernet 10G MAC (109 pages)

- LVDS SERDES Transmitter / Receiver (72 pages)

- Nios II Embedded Evaluation Kit Cyclone III Edition (3 pages)

- Nios II Embedded Evaluation Kit Cyclone III Edition (80 pages)

- IP Compiler for PCI Express (372 pages)

- Parallel Flash Loader IP (57 pages)

- Nios II C2H Compiler (138 pages)

- RAM-Based Shift Register (26 pages)

- RAM Initializer (36 pages)

- Phase-Locked Loop Reconfiguration IP Core (51 pages)

- DCFIFO (28 pages)