Altera Video and Image Processing Suite User Manual

Page 54

You can build logic (or program a Nios II processor) to control the gamma corrector as follows:

1. Set the

Go

bit to zero. This causes the IP core to stop processing at the end of the current frame.

2. Poll the

Status

bit until the IP core sets it to zero. This occurs at the end of the current frame, after the

IP core has stopped processing data.

3. Update the gamma look-up table.

4. Set the

Go

bit to one. This causes the IP core to start processing the next frame.

5. Poll the

Status

bit until the IP core sets it to one. This occurs when the IP core has started processing

the next frame (and therefore setting the

Go

bit to zero causes it to stop processing at the end of the

next frame).

6. Repeat steps 1 to 5 until all frames are processed.

This procedure ensures that the update is performed exactly once per frame and that the IP core is not

processing data while the update is performed.

When using IP cores which double-buffer control data, such as the Alpha Blending Mixer, a more simple

process may be sufficient:

1. Set the

Go

bit to zero. This causes the IP core to stop if it gets to the end of a frame while the update is

in progress.

2. Update the control data.

3. Set the

Go

bit to one.

The next time a new frame is started after the

Go

bit is set to one, the new control data is loaded into the IP

core.

The reading on non-video packets is performed by handling any packet until one arrives with type 0. This

means that when the

Go

bit is checked, the non-video type has been taken out of the stream but the video

is retained.

Specification of the Type of Avalon-MM Slave Interfaces

The Avalon-MM slave interfaces only use certain signals for Video and Image Processing Suite IP cores.

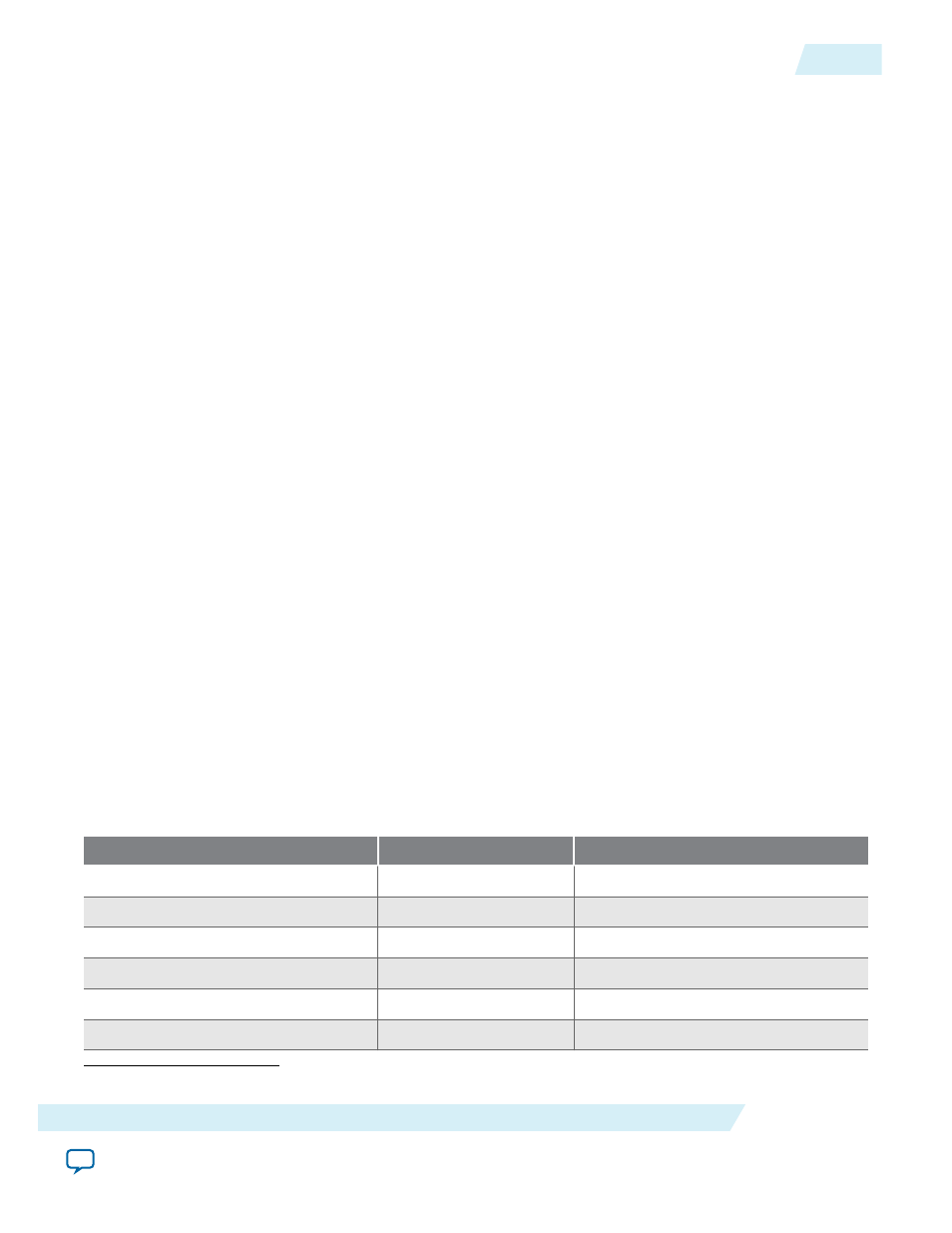

Table 2-12: Avalon-MM Slave Interface Signal Types

The table below lists the signals that the Avalon-MM slave interfaces use in the Video and Image Processing Suite.

The unused signals are not listed.

Note: The slave interfaces of the Video and Image Processing IP cores may use either

chipselect

or

read

.

Signal

Width

Direction

chipselect

1

Input

read

1

Input

address

Variable

Input

readdata

Variable

Output

write

1

Input

writedata

(5)

Variable

Input

(5)

For slave interfaces that do not have a predefined number of wait cycles to service a read or a write request.

UG-VIPSUITE

2015.05.04

Specification of the Type of Avalon-MM Slave Interfaces

2-27

Interfaces

Altera Corporation