Altera Video and Image Processing Suite User Manual

Page 307

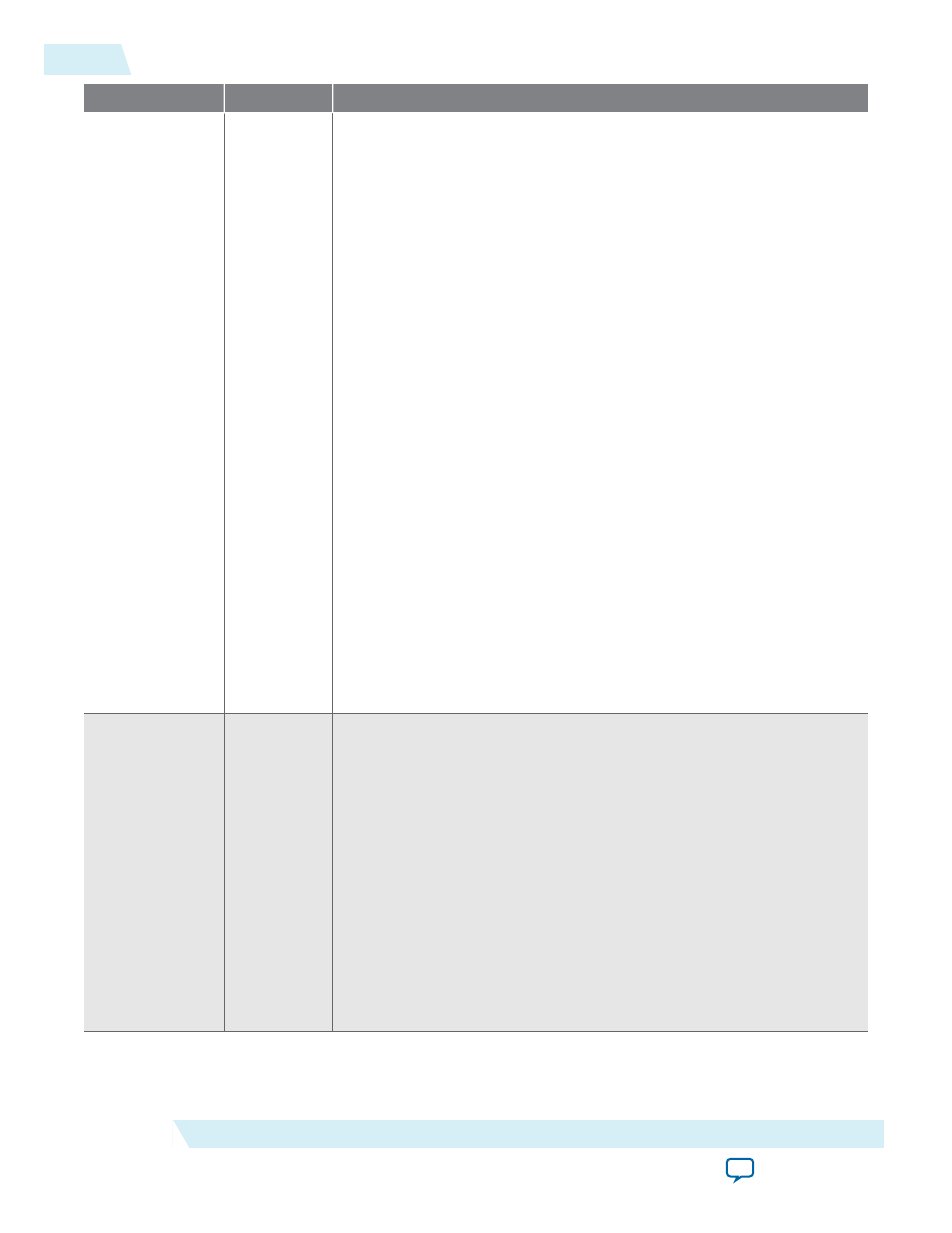

Date

Version

Changes

• Edited the parameter settings information for the Mixer II IP core.

• Added description for new parameter Pattern which enables you

to select the pattern for the background layer.

• Removed information about Color planes transmitted in

parallel . This feature is now default and internally handled

through the hardware TCL file.

• Edited the parameter settings information for the Frame Buffer II IP

core.

• Added descriptions for parameters that were not supported in the

previous version: Maximum ancillary packets per frame,

Interlace support, Locked rate support, Run-time writer

control, andRun-time reader control

• Removed information about Ready latency and Delay length

(frames). These features are fixed to 1 and internally handled

through the hardware TCL file.

• Edited the parameter settings information for the Avalon-ST Video

Monitor IP core.

• Added description for new parameters: Color planes transmitted

in parallel and Pixels in parallel.

• Removed information about the Number of color planes in

sequence parameter. You can specify whether to transmit the

planes in parallel or in series using the Color planes transmitted

in parallel parameter.

• Added a note that the Capture video pixel data feature only

functions if you specify the number of pixels transmitted in

parallel to 1.

January 2015

2015.01.23 • Added support for Arria 10 and MAX 10 devices. Arria 10 devices

support only the following IP cores: Avalon-ST Video Monitor,

Broadcast Deinterlacer, Clipper II, Clocked Video Input, Clocked

Video Input II, Clocked Video Output, Clocked Video Output II,

Color Space Converter II, Deinterlacer II, Frame Buffer II, Mixer II,

Scaler II, Switch II, and Test Pattern Generator II.

• Removed the Generate Display Port output parameter from the

Clocked Video Output II IP core. This feature is now default and

internally handled through the hardware TCL file.

• Added description for a new signal for Clocked Video Input II IP

core:

vid_hdmi_duplication[3:0]

.

• Added information for the missed out

Coeff-commit

control register

for the Color Space Converter II IP core.

• Edited the description for the Frame Buffer II parameters.

C-2

Document Revision History

UG-VIPSUITE

2015.05.04

Altera Corporation

Additional Information