1 os timer count register (oscr), 3 os timer watchdog match enable register (ower), Os timer count register (oscr) -22 – Intel STRONGARM SA-1100 User Manual

Page 92: Os timer watchdog match enable register (ower) -22, System control module, Sa-1100

9-22

SA-1100

Developer’s Manual

System Control Module

9.4.1

OS Timer Count Register (OSCR)

The OS timer count register is a 32-bit counter that increments on rising edges of the 3.6864-MHz

clock. This counter can be read or written at any time. It is recommended that the system

write-protect this register through the MMU protection mechanisms.

9.4.2

OS Timer Match Registers 0–3 (OSMR<0>, OSMR<1>,

OSMR<2>, OSMR<3>)

These registers are 32 bits wide and are readable and writable by the processor. They are compared

against the OSCR following every rising edge of the 3.6864-MHz clock. If any of these registers

match the counter at this time, then the corresponding status bit in the OSSR is set. The status bits

are routed to the interrupt controller where they can be unmasked to cause a CPU interrupt.

OSMR<3> may also serve as a watchdog timer. See the

Section 9.4.6, “Watchdog Timer” on

for operation information.

9.4.3

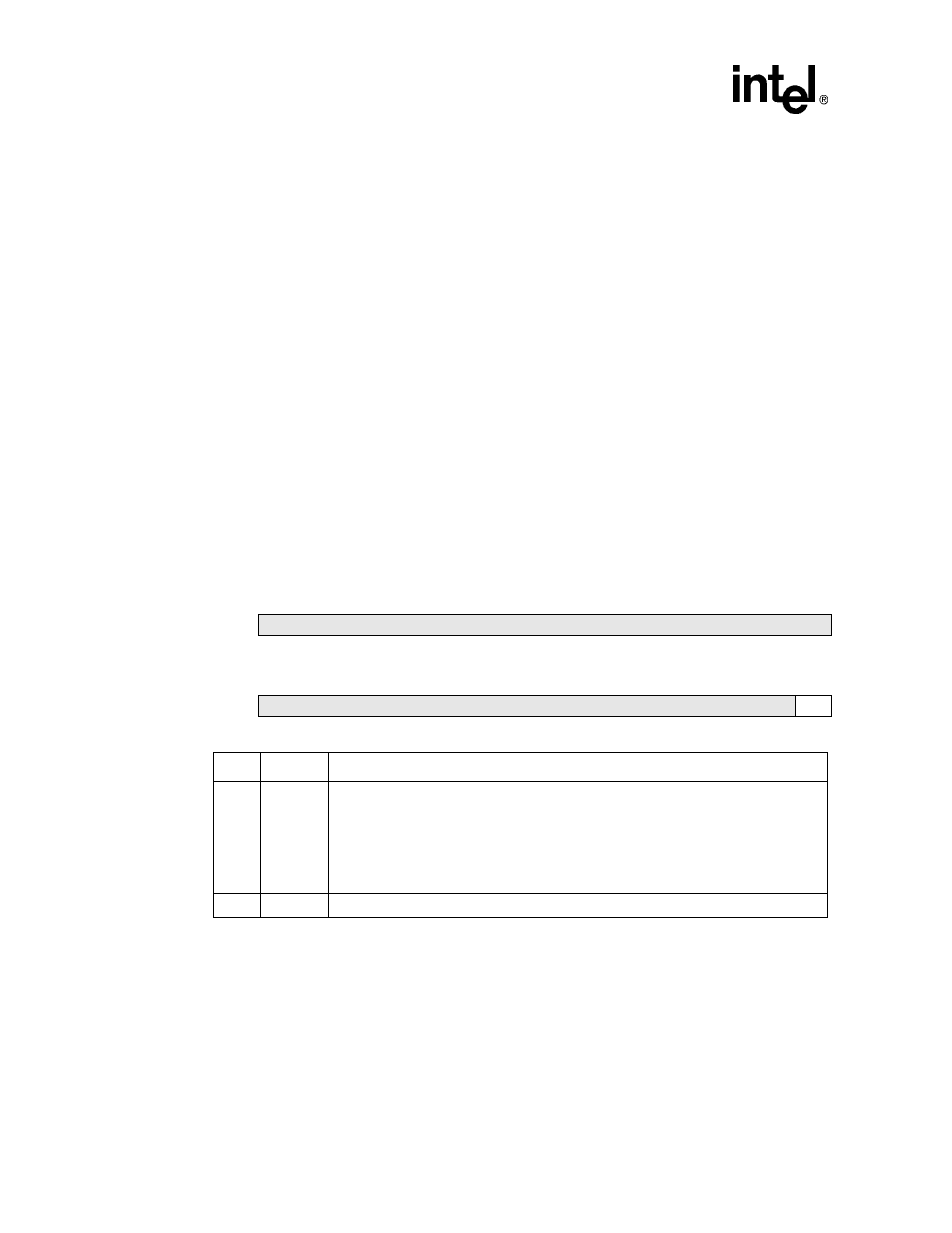

OS Timer Watchdog Match Enable Register (OWER)

The watchdog enable register contains a single control bit (bit 0) that enables the watchdog

function. This bit is set by writing a one to it. It can only be cleared by one of the reset functions

(hardware reset, software reset) and by entering sleep mode. A watchdog reset also clears the

watchdog enable bit. The format of this register follows:

.

Bit

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

R/W

Reserved

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

R/W

Reserved

WME

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bit

Name

Description

0

WME

Watchdog match enable.

0 – OS timer match register<3> matches cause an interrupt request.

1 – OS timer match register<3> matches cause a reset of the

SA-1100.

Note: This is a write-once bit that once written, can only be changed after a hardware

(pin), software (SWR), or sleep mode reset.

31..1

—

Reserved.