6 test data registers, 1 bypass register, Test data registers -5 16.6.1 bypass register -5 – Intel STRONGARM SA-1100 User Manual

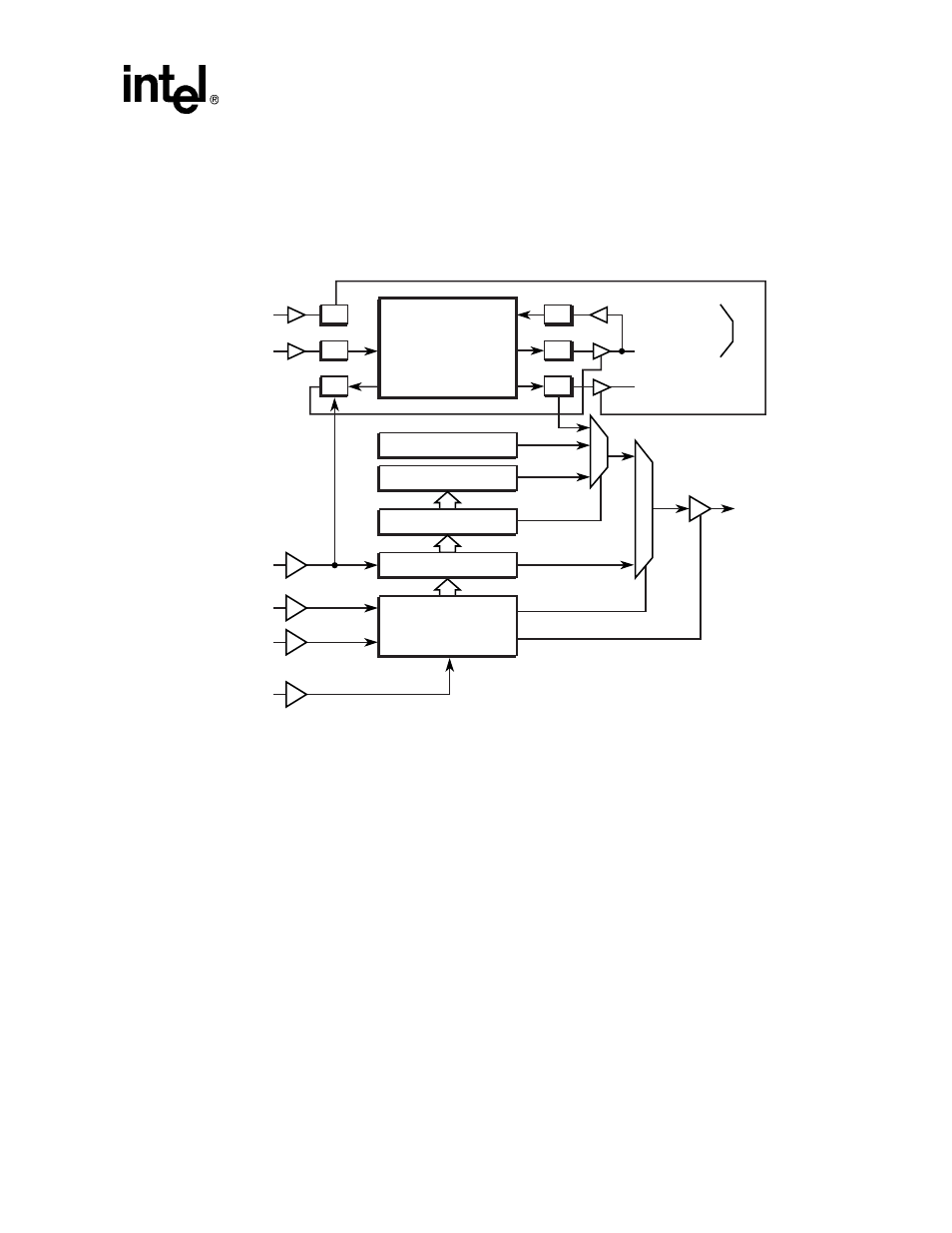

Page 365: Boundary-scan block diagram -5

SA-1100 Developer’s Manual

16-5

Boundary-Scan Test Interface

16.6

Test Data Registers

illustrates the structure of the boundary-scan logic.

Figure 16-2. Boundary-Scan Block Diagram

16.6.1

Bypass Register

Purpose: This is a single-bit register that can be selected as the path between TDI and TDO to

allow the device to be bypassed during boundary-scan testing.

Length: 1 bit

Operating Mode: When the BYPASS instruction is the current instruction in the instruction

register, serial data is transferred from TDI to TDO in the SHIFT-DR state with a delay of one TCK

cycle.

There is no parallel output from the bypass register.

A logic 0 is loaded from the parallel input of the bypass register in the CAPTURE-DR state.

A6839-01

* StrongARM is a registered trademark of ARM Limited.

BSINCELL

BSOUTCELL

BSOUTCELL

BSINENCELL

BSINCELL

BSOUTNENCELL

I/O

Cell

Intel

®

StrongARM

®

SA-1100

Device ID Register

Bypass Register

Instruction Decoder

TDO

TDI

TMS

TCK

nTRST

Instruction Register

nTDOEN

Core Logic

TAP

Controller