4 interrupt controller level register (iclr), 4 interrupt controller level register (iclr) -15, System control module – Intel STRONGARM SA-1100 User Manual

Page 85

SA-1100 Developer’s Manual

9-15

System Control Module

9.2.1.4

Interrupt Controller Level Register (ICLR)

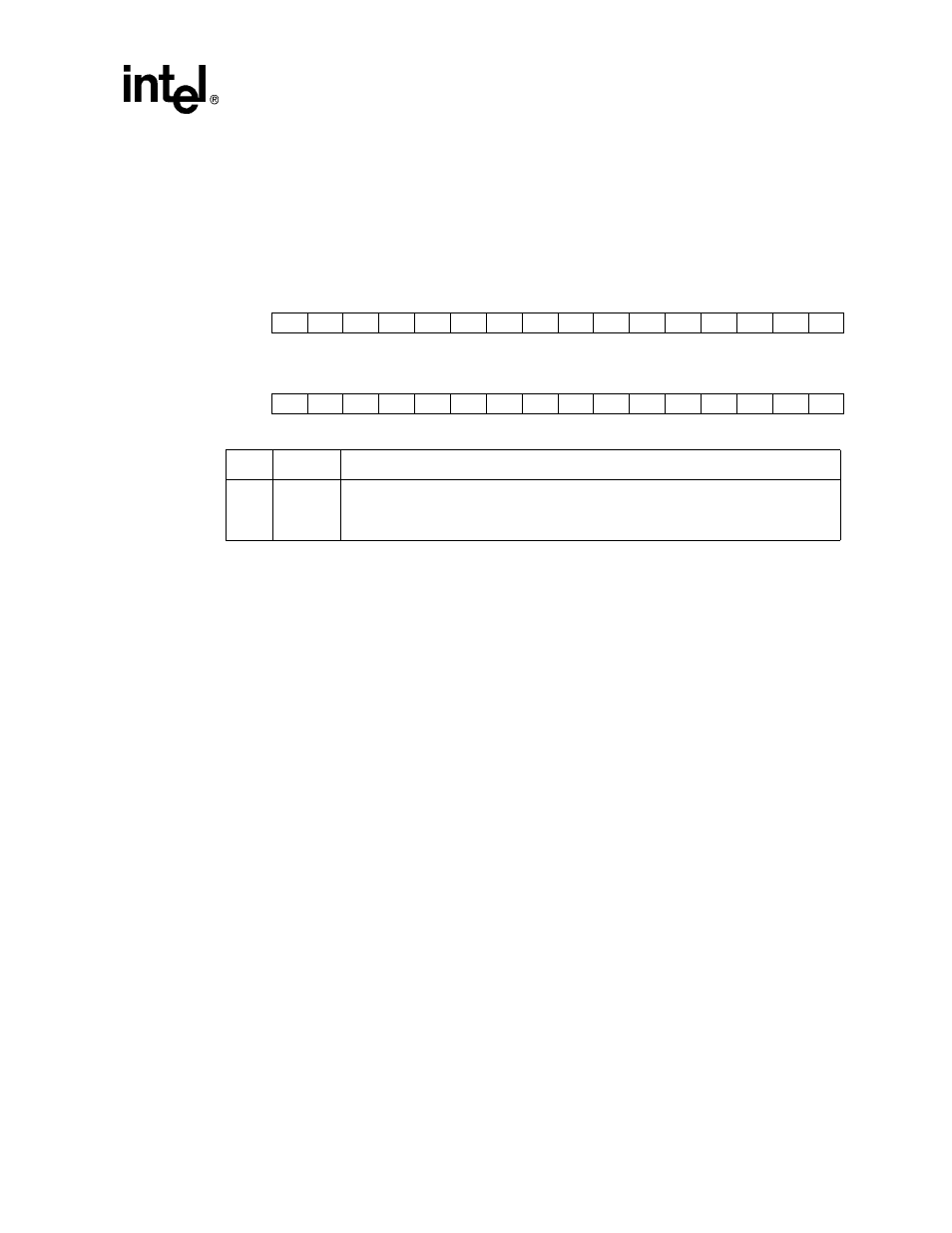

The interrupt controller level register (ICLR) controls whether a pending interrupt generates an

FIQ or an IRQ CPU interrupt. If a pending interrupt is unmasked, the corresponding ICLR bit field

is decoded to select which CPU interrupt should be asserted. If the interrupt is masked, then the

corresponding bit in the ICLR has no effect. The following table shows the location of all interrupt

level bits in the ICLR; question marks indicate that the values are unknown at reset.

Bit

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

R/W

IL31

IL30

IL29

IL28

IL27

IL26

IL25

IL24

IL23

IL22

IL21

IL20

IL19

IL18

IL17

IL16

Reset

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

R/W

IL15

IL14

IL13

IL12

IL11

IL10

IL9

IL8

IL7

IL6

IL5

IL4

IL3

IL2

IL1

IL0

Reset

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

Bit

Name

Description

{n}

IL{n}

Interrupt level n (where n = 0 through 31).

0 – Interrupt routed to CPU IRQ interrupt input.

1 – Interrupt routed to CPU FIQ interrupt input.