4 uart control registers 1 and 2, 1 baud rate divisor (brd), 4 uart control registers 1 and 2 -134 – Intel STRONGARM SA-1100 User Manual

Page 284: 1baud rate divisor (brd) -134

11-134

SA-1100

Developer’s Manual

Peripheral Control Module

11.11.4

UART Control Registers 1 and 2

UART control register 1 (UTCR1) contains the upper 4 bits and UTCR2 the lower 8 bits of the

baud rate divisor field.

11.11.4.1

Baud Rate Divisor (BRD)

The 12-bit baud rate divisor (BRD) field is used to select the baud or bit rate of the UART. A total

of 4096 different baud rates can be selected, ranging from a minimum of 56.24 bps to a maximum

of 230.4 Kb/ps. The baud rate generator uses the 3.6864-MHz clock generated by the on-chip PLL

divided by 16 to generate the bit clock. A digital PLL is used to synchronize the baud rate of the

receiver each time the start bit is detected on the receive pin and each bit of the receive data stream

is sampled on the eighth clock of the divide by 16 counter (halfway through the bit period). The

resultant baud rate, given a specific BRD value or required BRD value and given a desired baud

rate, can be calculated using the following two respective equations, where BRD is the decimal

equivalent of the binary value programmed within the bit field:

The following tables show the bit locations corresponding to the baud rate divisor field that is split

between two 8-bit registers. The upper four bits of BRD reside within UTCR1 and the lower eight bits

reside within UTCR2. The UART must be disabled (RXE=TXE=0) whenever these registers are written.

The reset state of the BRD field is unknown (indicated by question marks) and must be initialized before

enabling the UART. Note that writes to reserved bits are ignored and reads return zeros.

BaudRate

3.6864

6

×

10

16

x

BRD

1

+

(

)

---------------------------------------

=

BRD

3.6864

6

×

10

16

x

BaudRate

----------------------------------------

1

–

=

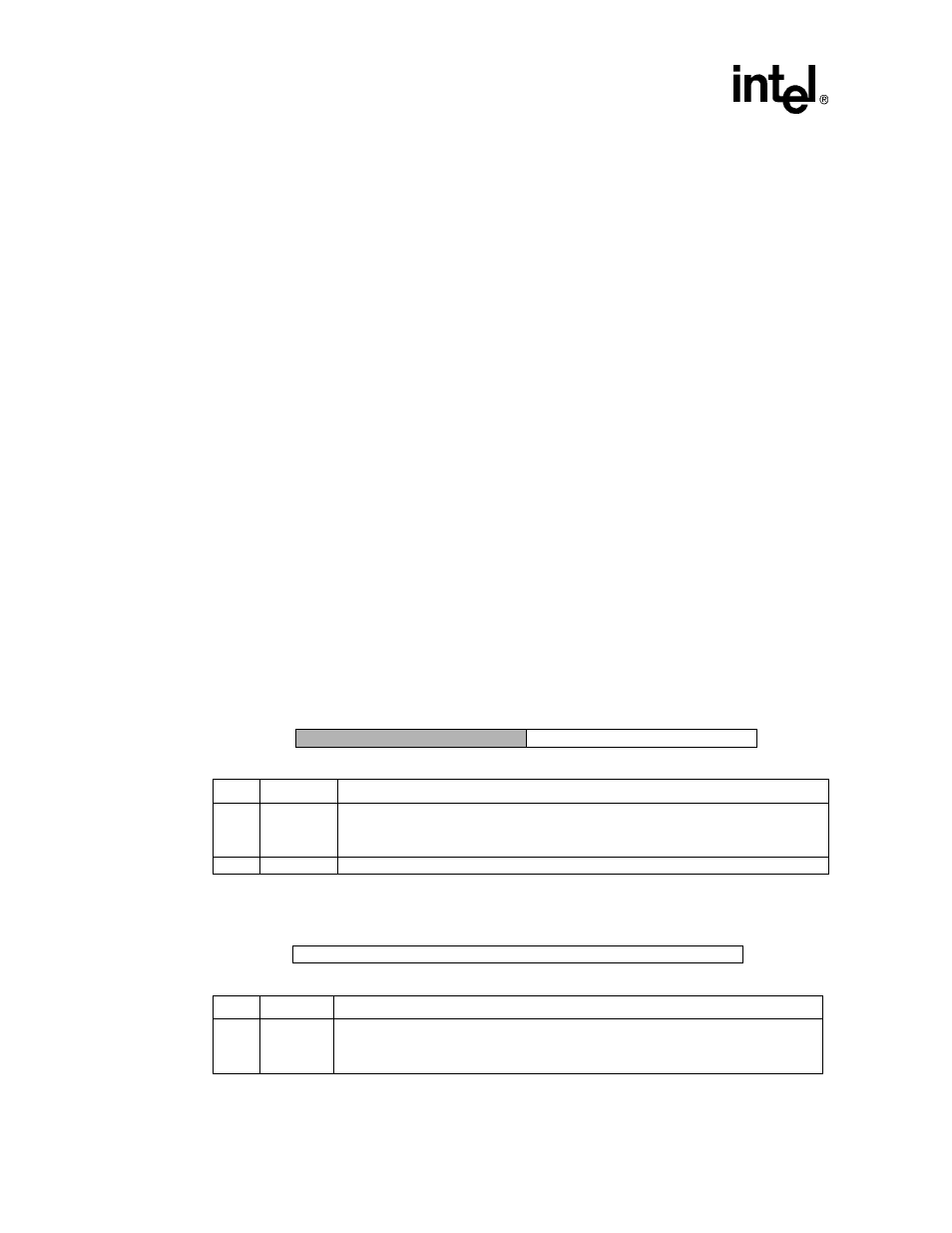

Address: 0h 8005 0004

UTCR1

Read/Write

Bit

7

6

5

4

3

2

1

0

Reserved

BRD<11:8>

Reset

0

0

0

0

?

?

?

?

Bit

Name

Description

3..0

BRD<11:8>

Baud rate divisor.

Encoded value (from 0 to 4096) used to generate the baud rate of the UART.

Baud Rate = 3.6864x10

6

/(16x(BRD+1)), where BRD is a decimal value.

7..4

—

Reserved.

Address: 0h 8005 0008

UTCR2

Read/Write

Bit

7

6

5

4

3

2

1

0

BRD<7:0>

Reset

?

?

?

?

?

?

?

?

Bit

Name

Description

7..0

BRD<7:0>

Baud rate divisor.

Encoded value (from 0 to 4096) used to generate the baud rate of the UART.

Baud Rate = 3.6864x10

6

/(16x(BRD+1)), where BRD is a decimal value.