1 cacheable reads (linefetches), 2 buffered writes, Cacheable reads (linefetches) -2 – Intel STRONGARM SA-1100 User Manual

Page 64: Buffered writes -2

7-2

SA-1100

Developer’s Manual

Memory-Management Unit (MMU)

7.3.1

Cacheable Reads (Linefetches)

A linefetch can be safely aborted on any word in the transfer. If an abort occurs during the

linefetch, the cache is purged so it will not contain invalid data. If the abort happens before the

word that was requested by the access is returned, the load is aborted. If the abort happens after the

word that was requested by the access is returned, the load completes and the fill is aborted (but no

exception is generated).

7.3.2

Buffered Writes

Buffered writes cannot be externally aborted. Therefore, the system should be configured such that it

does not perform buffered writes to areas of memory that are capable of flagging an external abort.

7.4

Interaction of the MMU, Icache, Dcache, and Write

Buffer

The MMU, Icache, Dcache, and WB can be enabled or disabled independently. The Icache can be

enabled with the MMU enabled or disabled. However, the Dcache and WB can only be enabled

when the MMU is enabled. Because the write buffer is used to hold dirty copy-back cached lines

from the Dcache, it must be enabled along with the Dcache. Therefore, only four of the eight

combinations of the MMU, Dcache, and WB enables are valid. There are no hardware interlocks

on these restrictions, so invalid combinations will cause undefined results.

The following procedures must be observed.

To enable the MMU:

1. Program the translation table base and domain access control registers.

2. Program level 1 and level 2 page tables as required.

3. Enable the MMU by setting bit 0 in the control register.

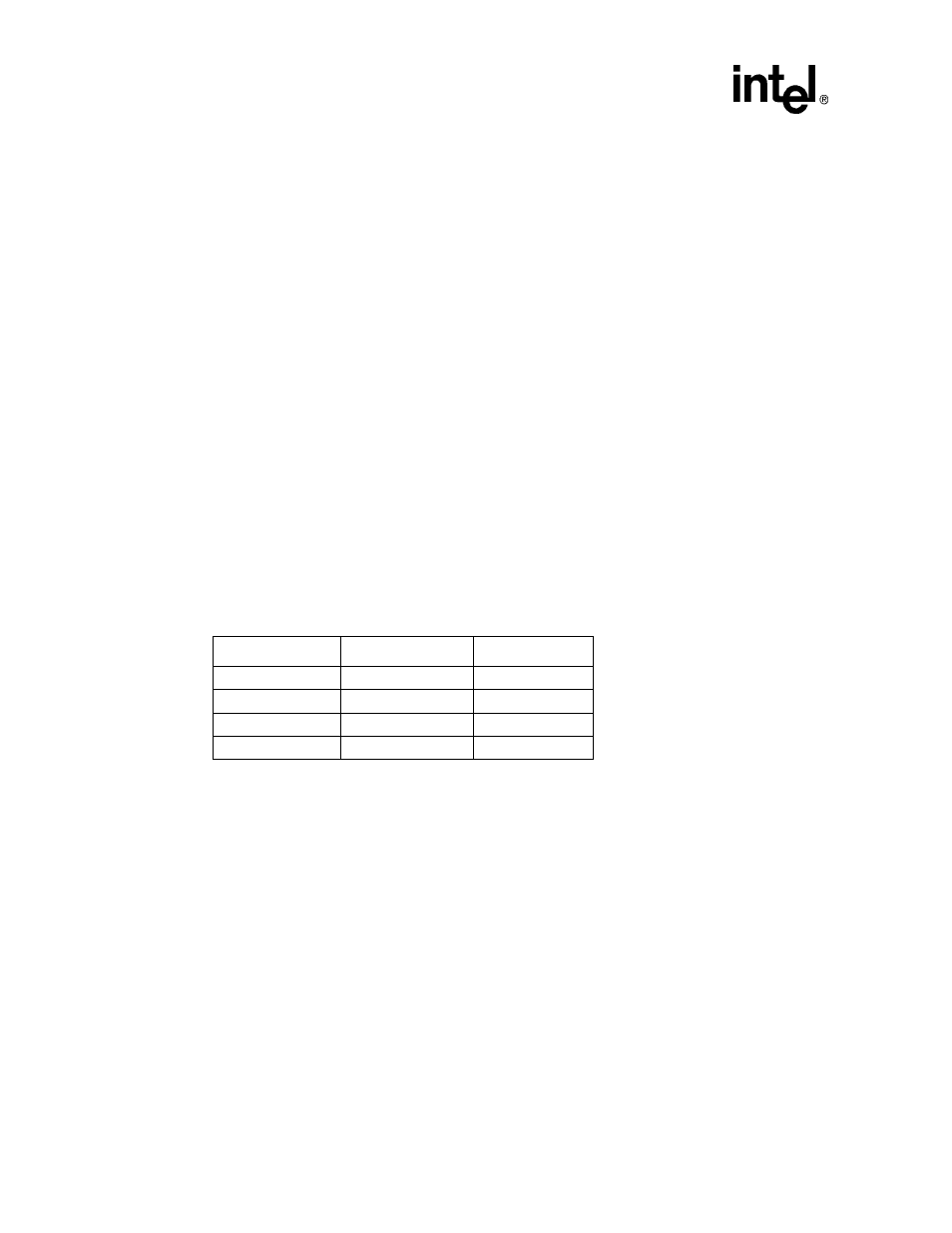

Table 7-1.

Valid MMU, Dcache, and Write Buffer Combinations

MMU

Dcache

Write Buffer

Off

Off

Off

On

Off

Off

On

Off

On

On

On

On