5 sdlc control register 2, 1 address match value (amv), 5 sdlc control register 2 -92 – Intel STRONGARM SA-1100 User Manual

Page 242: 1address match value (amv) -92

11-92

SA-1100

Developer’s Manual

Peripheral Control Module

11.9.5

SDLC Control Register 2

SDLC control register 2 (SDCR2) contains the 8-bit address match value field that is used by the

SDLC to selectively receive frames.

11.9.5.1

Address Match Value (AMV)

The 8-bit address match value (AMV) field is programmed with an address value that is used to

selectively store only the data within receive frames that have the same address value. The address

match enable (AME) bit must be set to enable this function. For incoming frames, which have the

same address value as the AMV field, the frame’s address, control, and data are stored in the

receive FIFO. For those that do not, the remainder of the frame is ignored, and the receive logic

looks for the next start flag in the incoming data stream. One special address exists that is always

matched by the address match logic regardless of the value programmed in AMV. When address

matching is enabled, whenever a frame is received with an address containing all ones (11111111),

the value programmed in AMV is ignored and the frame data is automatically stored in the receive

FIFO. The address value is contained within the first byte of data in a frame following the flag.

AMV can be written at any time, and is used for comparison for the next frame that occurs

following its update.

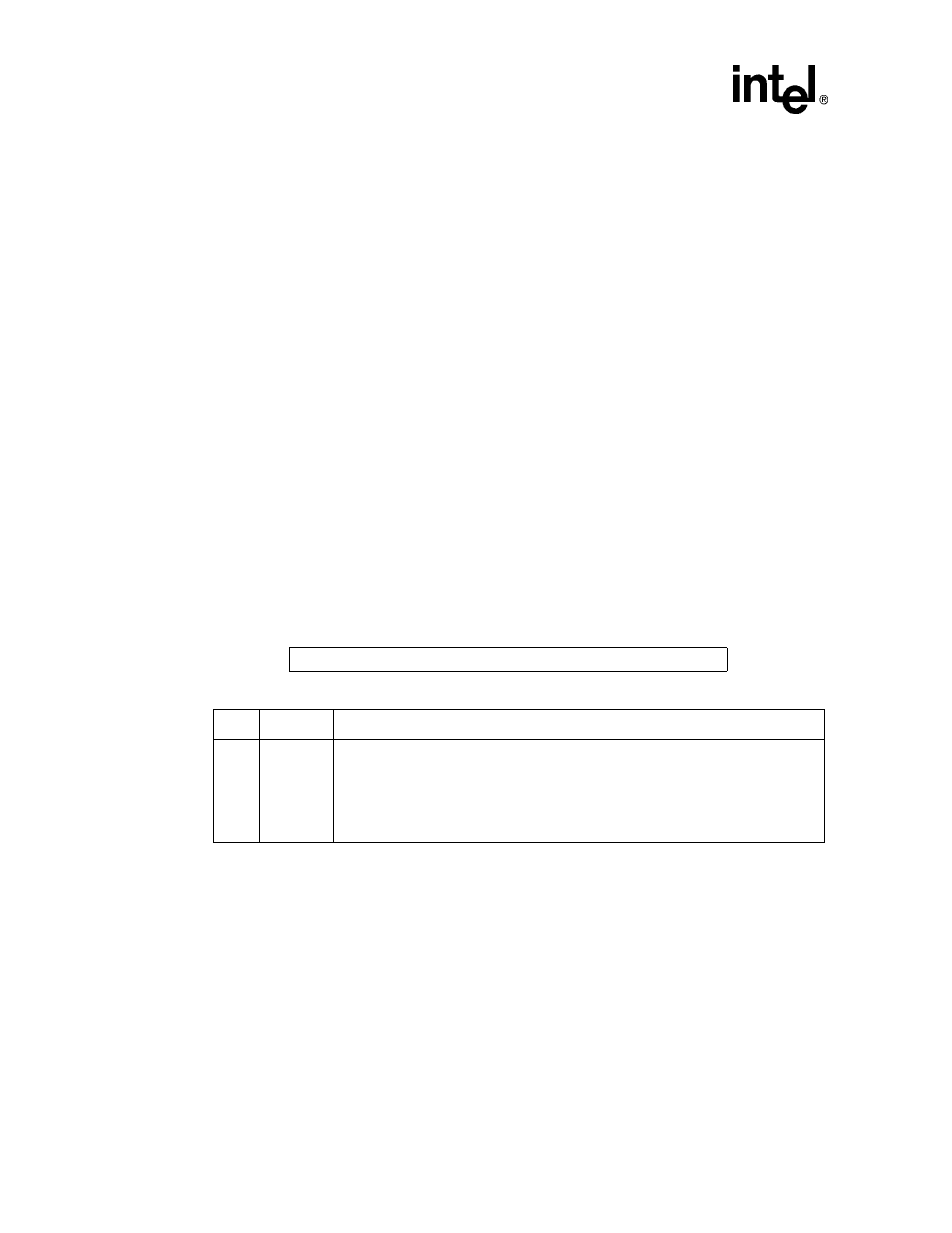

The following table shows the address match value field within SDLC control register 2. The reset

state of AMV is unknown (indicated by question marks) and must be initialized before enabling the

SDLC. Note that SDCR2 may be written while the SDLC is enabled to allow the address match

value to be changed during active receive operation.

Address: 0h 8002 0068

SDCR2

Read/Write

Bit

7

6

5

4

3

2

1

0

AMV

Reset

?

?

?

?

?

?

?

?

Bit

Name

Description

7..0

AMV

Address match value.

The 8-bit value used by receiver logic to compare to address of incoming frames. If

address matches, store frame address, control, and data in receive FIFO; if address

does not match, ignore frame and search for next flag.

Note: An address of 0hFF (all ones) in the incoming frame automatically generates a

match (AMV is ignored).