7 output enable polarity (oep), 7output enable polarity (oep) -41, Peripheral control module – Intel STRONGARM SA-1100 User Manual

Page 191

SA-1100 Developer’s Manual

11-41

Peripheral Control Module

11.7.6.7

Output Enable Polarity (OEP)

The output enable polarity (OEP) bit is used to select the active and inactive states of the output

enable signal in active display mode. In this mode, the ac bias pin is used as an enable that signals the

off-chip device when data is actively being driven out using the pixel clock. The pixel clock

continuously toggles during operation of active mode (PAS=1). When OEP=0, the L_BIAS pin is

active high and inactive low. When OEP=1, the L_BIAS pin is active low and inactive high. In active

display mode, data is driven onto the LCD’s data pins on the programmed edge of the L_PCLK pin

when L_BIAS is in its active state. Note that OEP does not affect L_BIAS in passive display mode.

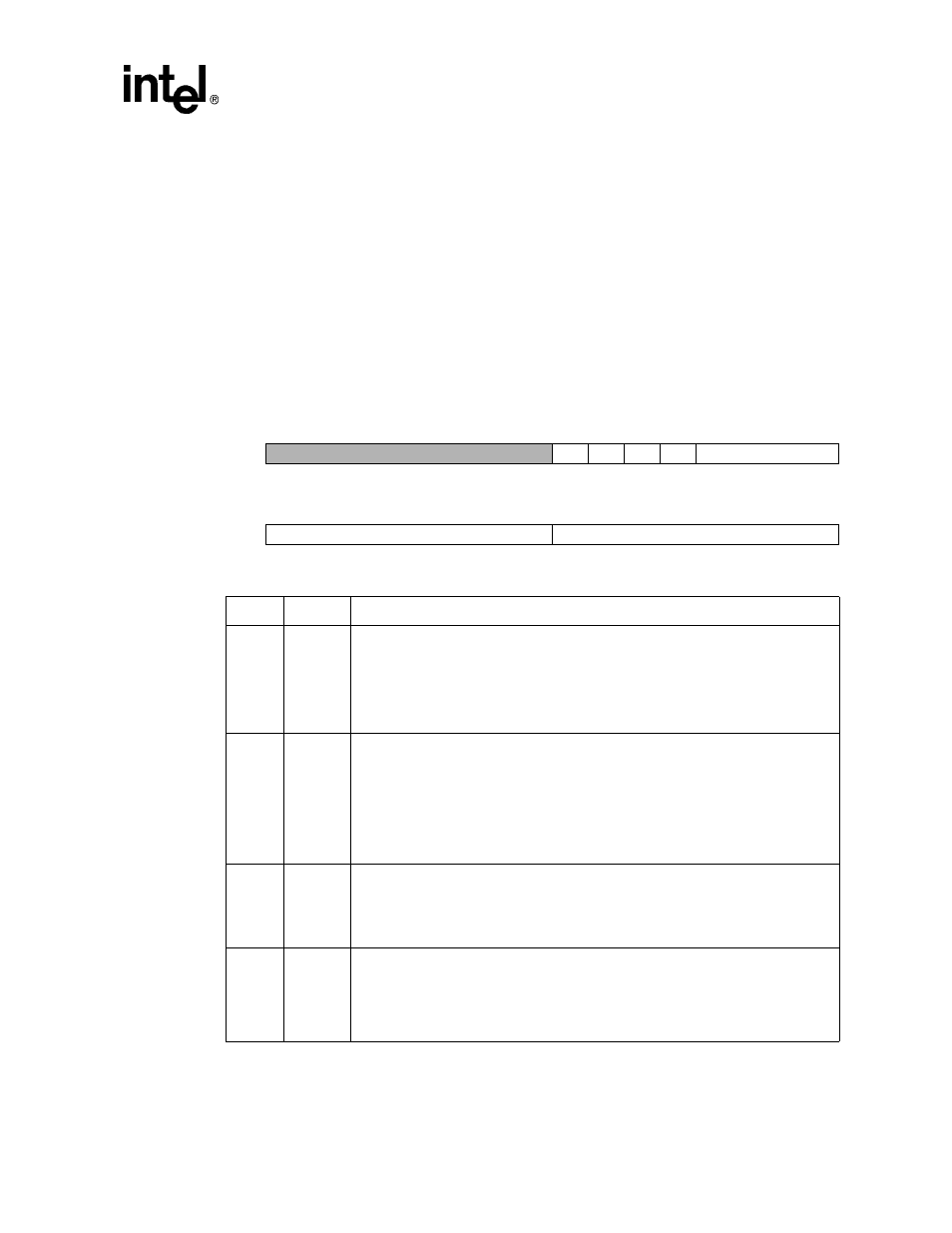

The following table shows the location of the seven different bit fields located in LCD controller

control register 3 (LCCR3). The LCD controller must be disabled (LEN=0) when changing the state

of any field within this register. Note that writes to reserved bits are ignored and reads return zeros.

Address: 0h B010 0028

LCCR3: LCD Controller Control Register 3

Read/Write

Bit

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

Reserved

OEP

PCP

HSP

VSP

API

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

-

-

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

ACB

PCD

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bit

Name

Description

7..0

PCD

Pixel clock divisor.

Value (from 0 to 255). Used to specify the frequency of the pixel clock based on the

CPU clock (CCLK) frequency. Pixel clock frequency can range from CCLK/6 to

CCLK/514.

Pixel Clock Frequency = CCLK/2(PCD+2).

Note that PCD must be programmed with a value of 1 or greater (PCD = 8’h00 is illegal).

15..8

ACB

AC bias pin frequency.

Value (from 1 to 256). Used to specify the number of line clocks to count before

transitioning the ac bias pin in passive mode (PAS=0). This pin is used to periodically

invert the polarity of the power supply to prevent dc charge buildup within the display. If

the passive display that is being controlled does not need to use L_BIAS, the user

should program ACB to its maximum value (8’hFF) to conserve power. Note that ACB

is ignored in active mode (PAS = 1).

Number of line clocks/toggle of the L_BIAS pin = (ACB+1).

19..16

API

AC bias pin transitions per interrupt.

Value (from 0 to 15). Used to specify the number of ac bias pin transitions to count

before setting the line count status (ABC) bit, signalling an interrupt request. Counter

frozen when ABC is set and is restarted when ABC is cleared by software. This

function is disabled when API=4’h0.

20

VSP

Vertical sync polarity.

0 – L_FCLK pin is active high and inactive low.

1 – L_FCLK pin is active low and inactive high.

Active mode: Vertical sync pulse active between frames, after end-of-frame wait period.

Passive mode: Frame clock active during first line of each frame.