Intel STRONGARM SA-1100 User Manual

Page 270

11-120

SA-1100

Developer’s Manual

Peripheral Control Module

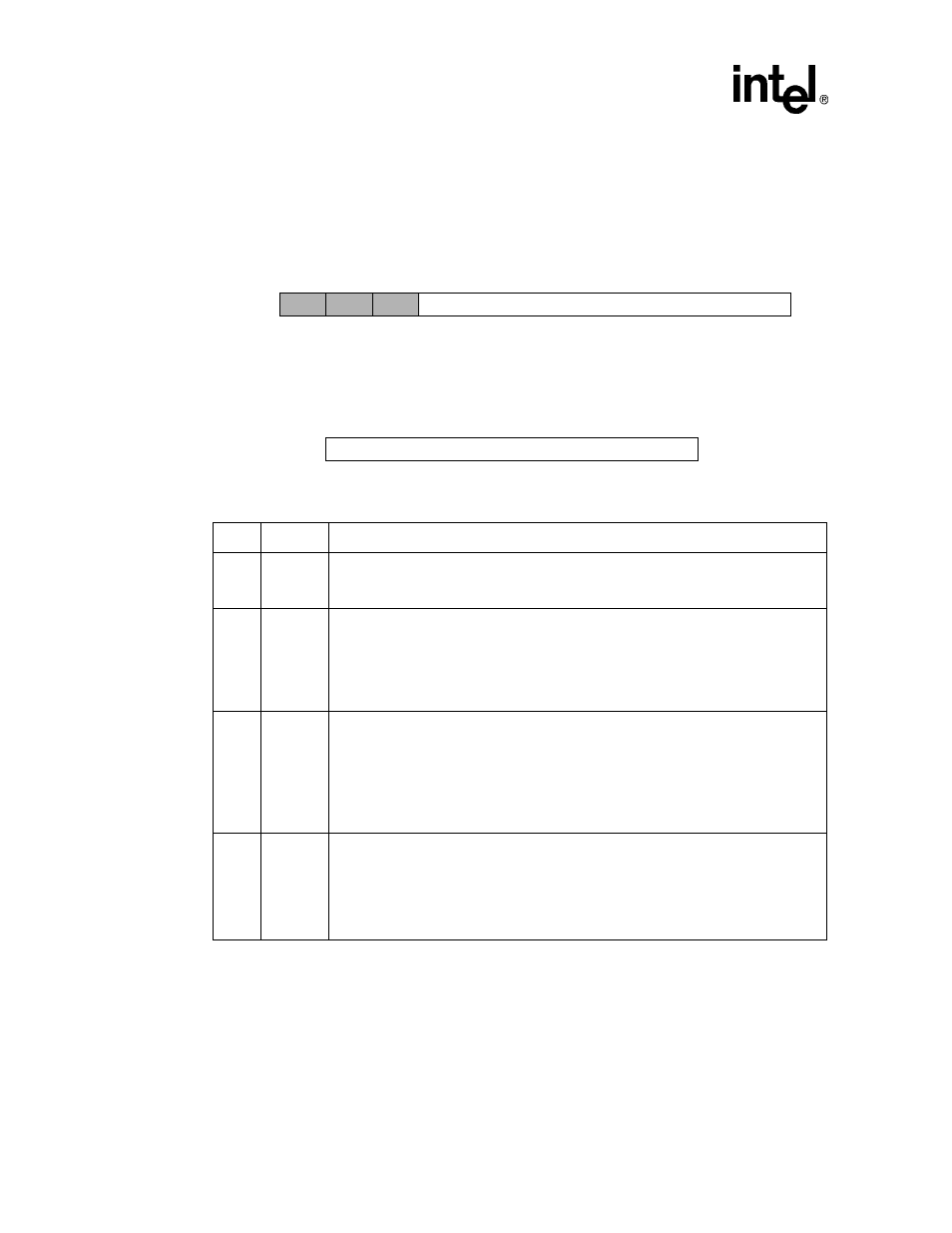

The following table shows the bit locations corresponding to the data field, end-of-frame bit as well

as the cyclic redundancy check and receiver overrun error bits within the HSSP data register. Note

that both FIFOs are cleared when the SA-1100 is reset, the transmit FIFO is cleared when TXE=0,

and the receive FIFO is cleared when RXE=0.

Address: 0h 8004 006C

HSDR

Read/Write

Bit

10

9

8

7

6

5

4

3

2

1

0

ROR

CRE

EOF

Bottom of receive FIFO data

Reset

0

0

0

0

0

0

0

0

0

0

0

Read Access

(Note: ROR, CRE, EOF are not read, but rather transferred to corresponding status bits in the HSSP

status register 1(HSSR1) each time a new data value is transferred to HSDR).

Bit

7

6

5

4

3

2

1

0

Top of transmit FIFO data

Reset

0

0

0

0

0

0

0

0

Write Access

Bit

Name

Description

7..0

DATA

Top/bottom of transmit/receive FIFO data.

Read – Bottom of receive FIFO.

Write –Top of transmit FIFO.

8

EOF

End of frame.

0 – The last byte of the frame has not been encountered.

1 – The data value at the bottom of the receive FIFO represents the last byte of the

frame.

Note: Each time an 11-bit value reaches the bottom of the receive FIFO, bit 8 from the

last FIFO entry is transferred to the EOF bit in HSSR1.

9

CRE

CRC error.

0 – CRC not encountered yet, or the CRC value calculated on the incoming data

matched the received CRC value.

1 – The CRC value calculated on the incoming data did not match the received CRC

value.

Note: Each time an 11-bit value reaches the bottom of the receive FIFO, bit 9 from the

last FIFO entry is transferred to the CRE bit in HSSR1.

10

ROR

Receiver overrun.

0 – No receiver overrun has been detected.

1 – Receive logic attempted to place data into receive FIFO while it was full; one or more

data values

after the data value at the bottom of the receive FIFO were lost.

Note: Each time an 11-bit value reaches the bottom of the receive FIFO, bit 10 from the

last FIFO entry is transferred to the ROR bit in HSSR1.